August 20th, 2019: Recent Progress in Carbon Nanotube Logic Technology

Recent Progress in Carbon Nanotube Logic Technology

Rebecca Park, PhD Candidate, Stanford University

Registration: HERE

Please register on Eventbrite before 8 PM on August 19

Tues August 20 – 11:30am: Networking & Pizza; Noon-1PM: Seminar

Cost: $4 to $6

Location: EAG Laboratories – 810 Kifer Road, Sunnyvale

ABSTRACT:

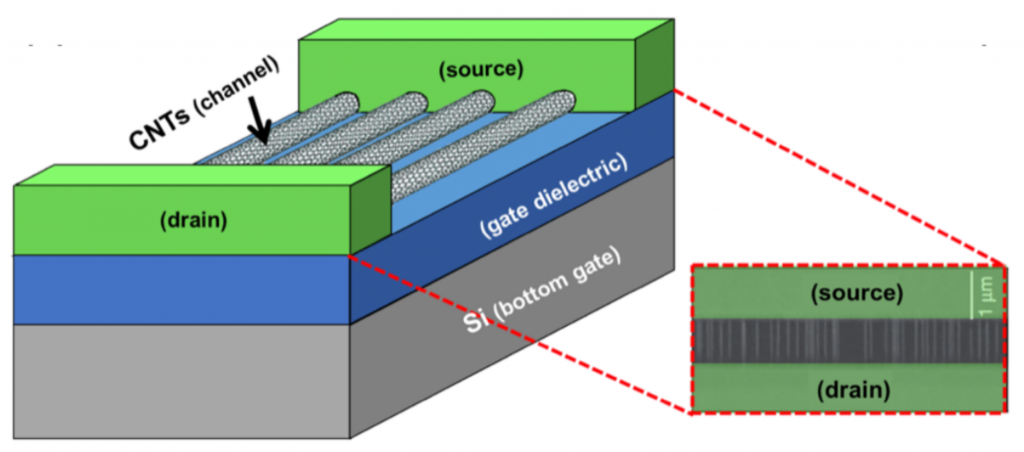

Tremendous effort has been made in exploring novel channel materials to complement silicon for future nanometer-scaled transistors. Among the viable options, carbon nanotubes (CNTs) are a potential candidate due to their high mobility and injection velocity despite their ultra-thin body thickness of 1 to 2 nm. Although carbon nanotube field-effect transistors (CNFETs) enable high-performance and energy-efficient digital systems, there are challenges that have yet to be solved.

In this talk, I will review the significant progress that has been made in recent years which has brought us closer to realizing the full benefits that the CNT technology promises.

BIOGRAPHY:

Rebecca Park received her B.S. from Cornell University in 2013 and is currently a Ph.D. candidate in Electrical Engineering at Stanford University, under the supervision of Professor H.-S. Philip Wong, co-advised by Professor Subhasish Mitra.

Her current research interest is in the development of high-performance and energy-efficient nanoelectronics, in which she has focused on carbon nanotube-based FETs.

Rebecca is a recipient of the Intel/SRCEA Masters Scholarship (2014-2016) and the Intel/SRCEA PhD Fellowship (2016-2019). Her internship experience includes working in the Science & Solutions team at IBM (2017 summer) and in the Flat Panel Displays team at Apple (2018 summer).