Past Events

Past Events

Welcome to Electron Devices Society–Santa Clara Valley/San Francisco Chapter

======================================================================

New CMOS-Compatible Materials for Efficient Infrared Light-Absorption and Emission

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Prof. Francesca Iacopi. The title of the lecture is ‘New CMOS-Compatible Materials for Efficient Infrared Light-Absorption and Emission’

When/Where: 14th Mar, 2024, 11:30 am. In-person event (Venue: EAG Laboratories – 810 Kifer Road, Sunnyvale)

(Use corner entrance: Kifer Road / San Lucar Court. Do not enter at main entrance on Kifer Road)

Note: MUST RSVP to attend in-person

Registration: Link

Speaker: Dr. Carlos Augusto

Abstract:

Efficient photon absorption and emission require semiconductors with direct bandgaps. Si and SiGe have indirect bandgaps and the wavelength range is determined by their bulk properties. Using proprietary ab-initio modeling, Quantum Semiconductor has invented atomistically-ordered superlattices made of Group IV elements (C, Si, Ge, Sn, Pb) strained to silicon surfaces, that have direct bandgaps across the infrared spectrum, and that can be monolithically integrated with CMOS. This approach overcomes the limitations of pure silicon devices – sensing light outside the visible range of wavelengths, and light emission. Also, the photon collection process is decoupled from CMOS junction engineering, thereby allowing these devices to track Moore’s Law with each new design generation, as well as use the most advanced substrates for state-of-the-art CMOS such as fully depleted thin-film SOI. This CMOS-compatible technology platform enables innovative new products for IR image sensing, photonics, and AI.

Read more: https://quantumsemi.com/

Speaker Bio:

Carlos Augusto, Ph.D., is a co-founder and the Chief Technology Officer of Quantum Semiconductor. A prolific inventor, he is responsible for Quantum Semiconductor’s core technology. Dr. Augusto has been in the semiconductor industry for over 25 years. Previously, he was at IMEC in Leuven, Belgium where he was a member of the research staff in the Advanced Silicon Devices Group and worked on the device, process, modeling and fabrication of SiGe Vertical MOSFETs and DRAMs. After IMEC, Dr. Augusto was recruited by Rockwell Semiconductor in Newport Beach, California and moved to the United States where he was in the Advanced Process Development Group and worked on device and process integration architecture development.

Carlos has a BSc. in Physics from the Instituto Superior Técnico, Technical University of Lisbon, Portugal, M.S. in Physics of Microelectronics and Materials Science, and Ph.D. in Electrical Engineering with a specialty in device physics from the Catholic University of Leuven, Belgium. He is the author or co-author of 32 granted and 2 pending US patents, covering Advanced CMOS devices and fabrication architectures, SiGeC Photo-Diodes and CMOS pixel designs and image-sensors, Group-IV superlattices and optoelectronic devices incorporating them.

Thanks to Eurofins EAG Laboratories for providing the venue for this seminar.

======================================================================

Ferroelectronics for next generation memory and NAND storage technology

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Prof. Asif Khan. The title of the lecture is ‘Ferroelectronics for next generation memory and NAND storage technology’

When/Where: 19th Jan, 2024, 12 noon. Hybrid event (Venue: Atherton Room, Plug and Play Tech Center, 440 N Wolfe Rd, Sunnyvale, CA 94085)

Note: MUST RSVP to attend in-person

Registration: Link

If you face an issue with vtools registration send an email to hiuyung.wong at ieee.org to get the zoom link and indicate whether you are an IEEE member, IEEE EDS member, IEEE Student member

Contact: hiuyung.wong at ieee.org

Speaker: Prof. Asif Khan

Abstract:

The rise of artificial intelligent (AI)-driven marvels hinges on the unrelenting advances in digital memory and storage solutions. The exponential trajectory of improvements of dynamic random-access memory (DRAM) and NAND flash, which are the mainstays of main memory and storage, respectively, is however facing formidable challenges at the technology level.

In this talk, we will discuss the potential of the emerging ferroelectric technologies to upend the DRAM and NAND landscapes [1-3]. We will highlight how ferroelectrics can enable the transition from 2-D to 3-D in DRAM technology and facilitate vertical scaling in NAND technology to achieve the 1000-layer milestone and beyond. We will also explore how ferroelectric devices can contribute to embedded and storage class memory technologies and examine the challenges they face.

[1] Asif Islam Khan, Ali Keshavarzi, and Suman Datta. “The future of ferroelectric field-effect transistor technology.” Nature Electronics 3.10 (2020): 588-597.

[2] Dipjyoti Das, Asif Khan et al. “Experimental Demonstration and Modeling of a Ferroelectric Gate Stack with a Tunnel Dielectric Insert for NAND Applications.” Proceedings of the 2023 IEEE International Electron Devices Meeting (IEDM).

[3] Nirmal Ramaswamy et al. “NVDRAM: A 32Gb Dual Layer 3D Stacked Non-volatile Ferroelectric Memory with Near-DRAM Performance for Demanding AI Workloads.” Proceedings of the 2023 IEEE International Electron Devices Meeting (IEDM).

Speaker Bio:

Asif Khan is an Associate Professor in the School of Electrical and Computer Engineering with a courtesy appointment in the School of Materials Science and Engineering at Georgia Institute of Technology. Dr. Khan’s research focuses on ferroelectric materials and devices to address the challenges faced by the semiconductor technology due to the end of transistor miniaturization. His work led to the first experimental proof-of-concept demonstration of the ferroelecric negative capacitance, which can reduce the power dissipation in transistors. His recent interest is understanding and demonstrating the fundamental limits of memory technologies concerning their scalability, density, capacity, performance, and reliability. His group publishes research on topics that include both logic and memory technologies, as well as artificial intelligence and neuromorphic hardware. Dr Khan’s notable awards include the DARPA Young Faculty Award (2021), the NSF CAREER award (2021), the Intel Rising Star award (2020), the Qualcomm Innovation Fellowship (2012), TSMC Outstanding Student Research Award (2011) and University Gold Medal from Bangladesh University of Engineering and Technology (2011). Dr. Khan received the Class of 1934 CIOS Honor Roll award for excellence in teaching a graduate course on Quantum Computing Devices and Hardware in Fall 2020. He is presently serving as an editor at IEEE Electron Device Letters. In the past, he has also worked as an associate editor for IEEE Access, and as a technical program committee member for various conferences including IEEE International Electron Devices Meeting (IEDM) and Design Automation Conference (DAC), among others.

======================================================================

European Open Source PDK Initiative Technology – Devices – Applications

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Dr. Wladek Grabinski. The title of the lecture is ‘FOSS TCAD/EDA Tools SPICE and Verilog – A Modeling Flow’

When/Where: Refer registration link (available early Dec)

Registration:Link

If you face an issue with vtools registration send an email to hiuyung.wong at ieee.org to get the zoom link and indicate whether you are an IEEE member, IEEE EDS member, IEEE Student member

Contact: hiuyung.wong at ieee.org

Speaker: Dr. Wladek Grabinski

Abstract:

Compact/SPICE models of circuit elements (passive, active, MEMS, RF, Microwave, Photonics) are essential to enable advanced IC design using nanoscaled semiconductor technologies. Compact/SPICE models are also a communication means between the semiconductor foundries and the IC design teams to share and exchange all engineering and design information. To explore all related interactions, we are discussing selected FOSS CAD tools along the complete technology/design tool chain from nanascaled technology processes; thru the compact modeling; to advanced IC transistor level design support. New technology and device development will be illustrated by application examples of the FOSS TCAD tools: Cogenda TCAD and DEVSIM. Compact modeling will be highlighted by review topics related to its parameter extraction and standardization of the experimental and measurement data exchange formats. Application and use of these tools for advanced IC design (e.g. analog/RF, Microwave, Photonics applications) directly depends on the quality of the compact model implementations in these tools as well as reliability of extracted models and generated libraries/PDKs. Discussing new model implementation into the FOSS CAD tools (Gnucap, Xyce, ngspice and Qucs as well as others) we will also address an open question of the compact/SPICE model Verilog-A standardization. We hope that this presentation will be useful to all the researchers and engineers actively involved in the developing compact/SPICE models as well as designing the integrated circuits in particular at the semiconductor device level and then trigger further discussion on the compact/SPICE model Verilog-A standardization and development supporting FOSS CAD tools.

Speaker Bio:

Wladek Grabinski received the Ph.D. degree from the Institute of Electron Technology, Warsaw, Poland, in 1991. From 1991 to 1998 he was a Research Assistant at the Integrated Systems Lab, ETH Zürich, Switzerland, supporting the CMOS and BiCMOS technology developments by electrical characterization of the processes and devices. From 1999 to 2000, he was with LEG, EPF Lausanne, and was engaged in the compact MOSFET model developments supporting numerical device simulation and parameter extraction. Later, he was a technical staff engineer at Motorola, and subsequently at Freescale Semiconductor, Geneva Modeling Center, Switzerland. He is now a consultant responsible for modeling, characterization and parameter extraction of MOS transistors for the design of RF CMOS circuits. He is currently consulting on the development of next-generation compact models for the nanoscaled technology very large scale integration (VLSI) circuit simulation. His current research interests are in high-frequency characterization, compact modeling and its Verilog-A standardization as well as device numerical simulations of MOSFETs for analog/RF low power IC applications. He is an editor of the reference modeling book Transistor Level Modeling for Analog/RF IC Design, and also authored or coauthored more than 70 papers. Wladek has established ESSDERC TPC Track3: “Device and circuit compact modeling” as well as was serving as a member of the IEEE EDS Compact Modeling Technical Committee, European representative in the ITRS Modeling and Simulation Working Group; organization committees of ESSDERC/ESSDERC, TPC of SBMicro, SISPAD, MIXDES Conferences; reviewer of the IEEE TED, IEEE MWCL, IJNM, MEE, MEJ. He was a Member At Large of Swiss IEEE ExCom and mentor of the EPFL IEEE Student Branch, now. Wladek is involved in activities of the MOS-AK Association and serves as a coordinating R&D manager since 1999.

======================================================================

Some efforts toward the modeling of integrated antennas

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Dr. Roberto S. Murphy. The title of the lecture is ‘Some efforts toward the modeling of integrated antennas’

When/Where: Refer registration link (available early Dec)

Registration:Link

If you face an issue with vtools registration send an email to hiuyung.wong at ieee.org to get the zoom link and indicate whether you are an IEEE member, IEEE EDS member, IEEE Student member

Contact: hiuyung.wong at ieee.org

Speaker: Dr. Roberto S. Murphy

Abstract:

With the development of faster, reliable and proven silicon based technologies, it is now possible to integrate antennas on chip (AoC), even though the semiconductor substrate is not the most convenient one for antenna applications. Nevertheless, an important number of research groups worldwide have made considerable advances in this field. Among many of the aspects being worked upon, the compact modeling of antennas outspends. The aim is to have SPICE compatible models in order to simulate the complete circuit as one, and avoid having different simulations and sets of parameters for the circuit and the antenna. In this talk, I will present some of the aspects that the group at INAOE (Puebla, Mexico)

has been tackling towards this end.

Speaker Bio:

Roberto S. Murphy-Arteaga received his B.Sc. degree in Physics from St. John’s University, Minnesota, and got his M.Sc. and Ph.D. degrees from the National Institute for Research on Astrophysics, Optics and Electronics (INAOE), in Tonantzintla, Puebla, México. He has been a researcher at INAOE since 1988. Since then, he has presented over 140 talks at scientific conferences, directed twelve Ph.D. dissertations, 20 M.Sc. and 3 B.Sc. theses, published more than 160 articles in scientific journals, conference proceedings and newspapers, and is the author of a text book on Electromagnetic Theory. His research interests are the physics, modeling and characterization of the MOS Transistor and passive components for high frequency applications, especially for CMOS wireless circuits, as well as antenna design for wireless communications. He is a member of the Mexican Academy of Sciences, of the Mexican National System of Researchers (SNI), as well as a Distinguished Lecturer of IEEE-EDS.

======================================================================

Investigating quantum speed limits with superconducting qubits

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Prof. Meenakshi Singh. The title of the lecture is ‘Investigating quantum speed limits with superconducting qubits’

When: Friday, Oct. 20, 2023 – 9am to 10am (PDT)

Where: This is an online event and attendees can participate via Zoom.

Registration:Link

If you face an issue with vtools registration send an email to hiuyung.wong at ieee.org to get the zoom link and indicate whether you are an IEEE member, IEEE EDS member, IEEE Student member

Contact: hiuyung.wong at ieee.org

Speaker: Prof. Meenakshi Singh

Abstract:

The speed at which quantum entanglement between qubits with short range interactions can be generated is limited by the Lieb-Robinson bound. Introducing longer range interactions relaxes this bound and entanglement can be generated at a faster rate. The speed limit for this has been analytically found only for a two-qubit system under the assumption of negligible single qubit gate time. We seek to demonstrate this speed limit experimentally using two superconducting transmon qubits. Moreover, we aim to measure the increase in this speed limit induced by introducing additional qubits (coupled with the first two). Since the speed up grows with additional entangled qubits, it is expected to increase as the system size increases. This has important implications for large-scale quantum computing.

Speaker Bio:

Dr. Singh is an experimental physicist with research focused on quantum thermal effects and quantum computing. She graduated from the Indian Institute of Technology with an M. S. in Physics in 2006 and received a Ph. D. in Physics from the Pennsylvania State University in 2012. Her Ph. D. thesis was focused on quantum transport in nanowires. She went on to work at Sandia National Laboratories on Quantum Computing as a post-doctoral scholar. She is currently an Associate Professor in the Department of Physics at the Colorado School of Mines. At Mines, her research projects include measurements of spin-orbit coupling in novel materials and thermal effects in superconducting hybrids. She recently received the NSF CAREER award to pursue research in phonon interactions with spin qubits in silicon quantum dots.

======================================================================

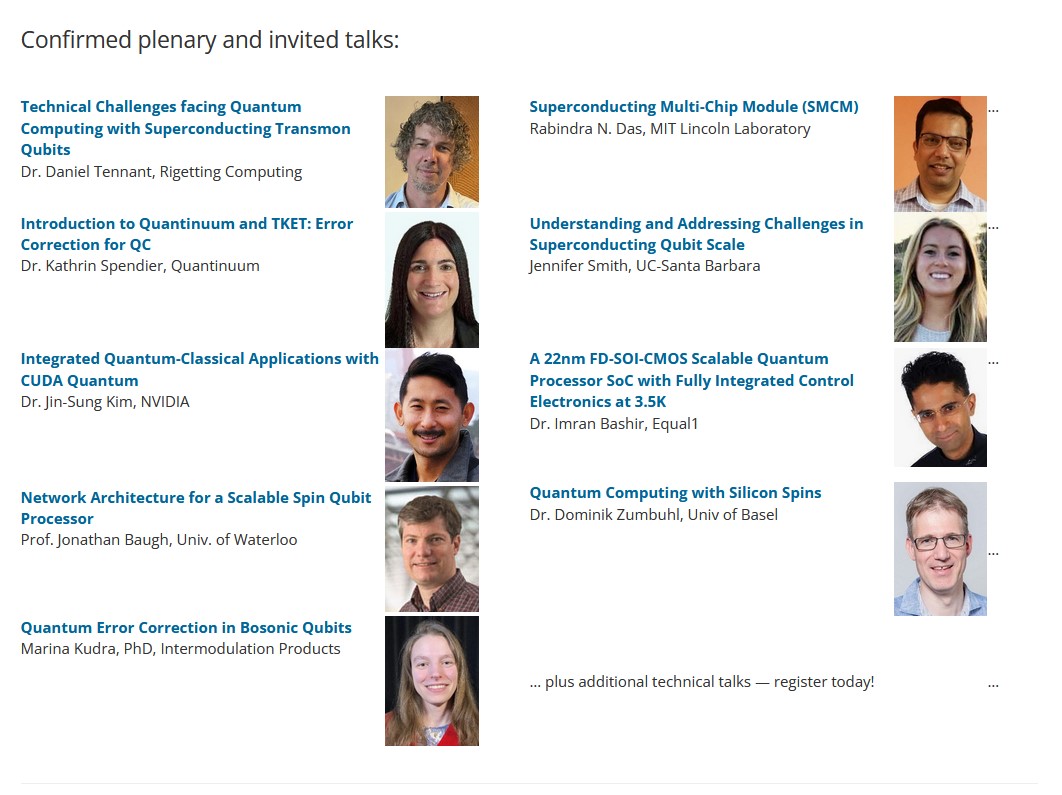

October 24-25, 2023, Quantum Computing: Devices, Cryogenic Electronics and Packaging (Link)

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is co-hosting this event.

When: Wednesday, September 20, 2023 – 3:30 pm to 5 pm (PDT)

Where: SEMI World Hdqtrs, Milpitas, CA USA

This is a hybrid event so speakers and attendees can choose to participate either in person or online

Registration Link: Here

Contact: hiuyung.wong at ieee.org

======================================================================

======================================================================

Defense Microelectronics Industrial Base

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is co-hosting this event. The title of the lecture is ‘Defense Microelectronics Industrial Base’

When: 25 Oct 2023, 06:30 PM to 08:00 PM (Eastern Time)

Where:

101 Maple Ave E, Vienna, Virginia

Building: Patrick Henry Library, Room Number: Meeting Room

If you wish to attend virtually, please register to receive the WebEx information.

Registration Link: Here

Contact: hiuyung.wong at ieee.org

Speaker: Dr. Clifford Lau of Institute for Defense Analyses

Abstract:

Semiconductor microelectronic chips are critical components in defense C4ISR and weapon systems. Department of Defense (DoD) needs to have an assured supply of advanced microcroelectronic chips, in peacetime and wartime. Since DoD itself normally does not make the chips, DoD depends on the semiconductor industry to produce the needed chips. DoD uses a variety of chips, many are commercial-off-the-shelf (COTS) and some are classified and defense-unique chips. The semiconductor industry, although originally created by DoD, for several decades has gradually moved off-shore, including fabrication, testing, and packaging. The U.S. market share of global semiconductor manufacturing capacity has fallen from about 38% in 1990 to 12% in 2020. TSMC in Taiwan is the world’s largest semiconductor chip manufacturer, supplying 92% of worlds sub-nanometer advanced chips. To bring semiconductor manufacturing back to the U.S., Congress passed the CHIPS and Science Act to reshore semiconductor manufacturing to the U.S. The CHIPS Act authorizes more than $200B, and immediately appropriates $53.7B, in federal funding to promote domestic semiconductor manufacturing production, DoD allocated $2B as a part of the CHIPS Act. DoD’s Microelectronics Commons initiative selected eight regional innovations hubs that include a large number of members in the industrial base. The objective of these hubs, called “lab to fab”, is to speed up the transition of microelectronics from research to prototyping to production, and is focused on strengthening the defense microelectronics industrial base.

Speaker Bio:

Dr. Clifford Lau is a research staff member at the Institute for Defense Analyses (IDA) performing studies and analyses to support the Office of Secretary of Defense and other defense and federal agencies. Prior to joining IDA, he spent a long career as scientific officer and program director in the Office of Naval Research (ONR) managing various basic science research programs in electronics, computers, and signal processing. He also spent six years as senior scientist at DDR&E managing the MURI, DURIP, and other defense S&T programs. He received his Ph.D. from UC Santa Barbara in 1978, M.S. from UC Berkeley in 1967, and B.S. from UC Berkeley in 1966, all in electrical engineering and computer science. He has published 56 papers and edited 7 books on neural networks and fault tolerant computing. In his 50 years of IEEE membership, he has served in various capacities, including serving as President of the IEEE Neural Networks Council (now the Computational Intelligence Society) in 1999-2000, President of the IEEE Nanotechnology Council in 2004, Vice President in Circuits and Systems Society in 1996-1997. He was a member of IEEE TAB in 1999-2000 and 2004. He served as associate editors and guest editors for various IEEE Transactions, including TNN, TAC, TCAS, and Proceedings. He was on the Editorial Board of the Proceedings of the IEEE in 1988-1996. He was General Chair for several major IEEE conferences, including IEEE-NANO and IJCNN. He was chair of IEEE-USA R&D Policy Committee in 2004-2006. In 2007 he was the IEEE-USA Vice President for Technology Policy. He is a Life Fellow of the IEEE.

======================================================================

CHIPS: An Unprecedented Opportunity What This Program Means

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is co-hosting this event. The title of the lecture is ‘CHIPS: An Unprecedented Opportunity What This Program Means’

When: Wednesday, September 20, 2023 – 3:30 pm to 5 pm (PDT)

Where:

101 Maple Ave E, Vienna, Virginia

Building: Patrick Henry Library, Room Number: Meeting Room

If you wish to attend virtually, please register to receive the WebEx information.

Registration Link: Here

Contact: hiuyung.wong at ieee.org

Speaker: Dr. Michael Fritze

Abstract:

Dr. Fritze will give his independent perspectives on what the CHIPS (Creating Helpful Incentives to Produce Semiconductors) Program means for the US particularly for the microelectronics community. He will cover the motivations behind this historic semiconductor investment and articulate the planned support level for each particular area. This includes the Department of Commerce Incentives and R&D efforts and the Department of Defense Microelectronics Commons. Particular attention will be paid to the R&D parts of this legislation. He will review the goals of this legislation in strengthening the US domestic microelectronics supply chain and R&D infrastructure. Dr. Fritze will also discuss some of the key challenges of this major US Government investment.

Speaker Bio:

Dr. Fritze is an independent technology consultant. He is a Senior Fellow and former Vice President at the Potomac Institute for Policy Studies. He is also a Consultant at Trusted Strategic Solutions. His interests include USG trusted microelectronics access strategies, support of needed legacy technologies, DOD innovation policy and outreach to Industry and strengthening the US Microelectronics Industrial Base. He has supported a variety of USG organizations primarily in the DoD on these issues.He is also a member of the Industrial Advisory Committee supporting the NIST CHIPS R&D efforts.

Dr. Fritze was the Director of the Disruptive Electronics Division at the USC Information Sciences Institute (2010-2015). He also held a Research Professor appointment in the USC Ming Hsieh Department of Electrical Engineering (Electrophysics). His research interests at ISI included Trusted Electronics, CMOS Reliability & Robustness, Low power 3DIC enabled electronics and Rad-hard electronics. He was a Program Manager at the DARPA Microsystems Technology Office (MTO) from 2006-2010. While at DARPA, Dr. Fritze was responsible for Programs in the areas of 3D Integrated Circuits (3DIC), Steep-Subthreshold-slope Transistors (STEEP), Radiation Hardening by Design (RHBD), Carbon Electronics for RF Applications (CERA), Silicon-based RF (TEAM), Ultra-low power Digital (ESE), Highly regular designs (GRATE) and Leading-edge foundry access (LEAP).

Prior to joining DARPA, Dr. Fritze was a staff member from 1995-2006 at MIT Lincoln Laboratory in Lexington, Massachusetts, where he worked on fully-depleted silicon on insulator (FDSOI) technology, silicon-based integrated optics and development and resolution-enhanced optical lithography.

Dr. Fritze received a Ph.D. in Physics from Brown University in 1994, working in the area of compound semiconductor quantum well physics. He received a B.S. in Physics in 1984 from Lehigh University. Dr. Fritze is an elected member of Tau Beta Pi and Sigma Xi. He is a recipient of the Office of the Secretary of Defense Medal for Exceptional Public Service awarded in 2010. He is a Senior Member of the IEEE and is active on the GOMAC Conference Program Committee as well as the NDIA Electronics Division Policy Group. Dr. Fritze has published over 75 papers and articles in professional journals and holds several U.S. Patents.

======================================================================

August 14-16, 2023, 5th IEEE International Flexible Electronics Technology Conference (IFETC) 2023 (Link)

======================================================================

======================================================================

What Are 2D Materials Good For?

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting Prof. Eric Pop. The title of the lecture is ‘What Are 2D Materials Good For?’

When: Friday, July 28, 2023 – 12 Noon to 1 pm (PDT)

Where: This is an online event and attendees can participate via Zoom.

Registration Link: Here

Contact: hiuyung.wong at ieee.org

Speaker: Prof. Eric Pop

Abstract:

This talk will present my (biased!) perspective of what two-dimensional (2D) materials could be good for. For example, they could be good for applications where their ultrathin nature gives them distinct advantages, such as flexible electronics [1] or light-weight solar cells [2]. They may not be good where conventional materials work sufficiently well, like transistors thicker than a few nanometers. I will focus on 2D materials for 3D heterogeneous integration of electronics, which presents major advantages for energy-efficient computing [3]. Here, 2D materials could be monolayer transistors with ultralow leakage [4] (due to larger band gaps than silicon), used to access high-density memory [5]. Recent results from our group [6,7] and others [8] have shown monolayer transistors with good performance, which cannot be achieved with sub-nanometer thin conventional semiconductors, and the 2D performance could be further boosted by strain [9]. I will also describe some unconventional applications, using 2D materials as thermal insulators [10], heat spreaders [11], and thermal transistors [12]. These could enable control of heat in “thermal circuits” analogous with electrical circuits. Combined, these studies reveal fundamental limits and some unusual applications of 2D materials, which take advantage of their unique properties.

Refs: [1] A. Daus et al., Nat. Elec. 4, 495 (2021). [2] K. Nassiri Nazif, et al., Nat. Comm. 12, 7034 (2021). [3] M. Aly et al., Computer 48, 24 (2015). [4] C. Bailey et al., EMC (2019). [5] A. Khan et al. Science 373, 1243 (2021). [6] C. English et al., IEDM, Dec 2016. [7] C. McClellan et al. ACS Nano 15, 1587 (2021). [8] S. Das et al., Nat. Elec. 4, 786 (2021). [9] I. Datye et al., Nano Lett. 22, 8052 (2022). [10] S. Vaziri et al., Science Adv. 5, eaax1325 (2019). [11] C. Koroglu & E. Pop, IEEE Elec. Dev. Lett. 44, 496 (2023). [12] M. Chen et al., 2D Mater. 8, 035055 (2021).

.

Speaker Bio:

Eric Pop is the Pease-Ye Professor of Electrical Engineering (EE) and Materials Science & Engineering (by courtesy) at Stanford, where he leads the SystemX Heterogeneous Integration focus area and the EE Culture, Equity, and Inclusion committee. His research interests include nanoelectronics, data storage, and energy. Before Stanford, he spent several years on the faculty of UIUC, and in industry at Intel and IBM. He received his PhD in EE from Stanford (2005) and three degrees from MIT in EE and Physics. His awards include the PECASE from the White House, and Young Investigator Awards from the Navy, Air Force, NSF CAREER, and DARPA. He is an APS and IEEE Fellow, an Editor of 2D Materials, and a Clarivate Highly Cited Researcher. In his spare time he enjoys snowboarding and tennis, and in a past life he was a college radio DJ at KZSU 90.1. More information about the Pop Lab is available at http://poplab.stanford.edu and on Twitter @profericpop..

======================================================================

======================================================================

EDS DL Event: Artificial Intelligence and Brain Biofields Quantum Computing

The Electron Devices Society Santa Clara Valley/San Francisco joint Chapter is hosting an EDS Distinguished Lecturer Dr. Adam Skorek. The titled of the lecture is ‘Artificial Intelligence and Brain Biofields Quantum Computing.

When: Friday, May 19, 2023 – 12 Noon to 1 pm (PDT)

Where: This is an online event and attendees can participate via Zoom.

Registration Link: Here

Contact: hiuyung.wong at ieee.org

Speaker: Prof. Adam Skorek (EDS Distinguished Lecturer)

Abstract:

Artificial intelligence (AI) is present in electrical, electronics, and computer engineering for years. In particular, the biofields defined as electromagnetics and thermal fields in living matter are naturally related to AI studies and applications, including brain analysis with numerical modeling and simulations. Brain functionalities inspire all developments in AI from theoretical investigations to machine learning, humanoids robots, Digital Twins (DT), and brains interface devices implementation. The brain biofields’ interactions with external excitations such as 5G/6G telecommunications devices, transcranial magnetic stimulation, and even other brains biofields are currently explored more than ever before. The computation demand in modeling and simulation is still growing and it is particularly high in both AI and brain biofields applications. Hopefully, the High-Performance Computing (HPC) and High-Performance Quantum Computing (HPQC) infrastructures become more easily accessible and offer researchers some new opportunities based on the open and shared resources including not only computing facilities with quantum units but also knowledge with currently observed openings in the field of intellectual property issues. A presentation from a worldwide perspective of some modern research works with their results applications is completed by the lecturer’s experiences and guidelines for the future. Some practical examples and instructions for researchers, engineers, and students are presented, stimulating the audience to various scientific as well R&D activities in those so promising areas.

Speaker Bio:

Prof. Adam Waldemar Skorek (M’87, SM’90, F’09, LF’23) completed Bachelor and Master of Electrical Engineering Program at Białystok University of Technology (Poland) receiving both Master and Engineer degrees in 1980. Participant of the Electrical Engineering Faculty Doctoral Studies, he received a Doctor of Technical Sciences degree in Electrical Engineering at Warsaw University of Technology (Poland) in 1983. From 1983 to 1987 he was a Visiting Lecturer at the Institute of Telecommunications in Oran (Algeria). In 1987, he joined the University of Quebec at Trois-Rivières (UQTR), Canada, where currently, he is a Full Professor and Director of the UQTR’s Electro-Thermal Management Laboratory which succeeded both the Nano-Heat Laboratory and Industrial Electro-Heat Laboratory, all founded and directed by himself since 1989. He is conducting electrical engineering courses for bachelor, master, and Ph.D. students. His research works were granted by NSERC, CFI, FRQNT, MITACS, and Industry. He was made contributions to the numerical analysis of electro-thermal and biofields phenomena exploring and applying various techniques to electrical apparatus, electronic devices, and living organisms. His publications and communications record include works on High-Performance Computing, Artificial Intelligence, Digital Twins (DT) and Quantum Computing applications, in electro-thermal and biofields analysis. A number of those publications are available in IEEE Xplore. The IEEE Life Fellow, as well as Fellow of the Engineering Institute of Canada, Prof. Adam W. Skorek is a Member of the Engineering Academy in Poland and recipient of the 2021 IEEE Industry Applications Society Distinguished Service Award.

======================================================================

======================================================================

IEEE SCV-SF EDS Mini Colloquium (March 24, 2023)

The Electron Devices Society Santa Clara Valley/San Francisco Chapter with the San Jose State University IEEE student chapter is hosting a mini-colloquium celebrating the 75th anniversary of the invention of the transistor. In this mini-colloquium, we are inviting 3 speakers to each give talks on topics ranging from traditional/planar transistors and advanced transistors to analog technology.

When: Friday, March 24, 2023 – 12 Noon to 2 pm (PST)

Where: This is a hybrid event so speakers and attendees can choose to participate either in person at SJSU Engineering building Rm. ENGR 376 or online via Zoom (link will be sent after registration).

Registration Link: Here

Contact: hiuyung.wong at ieee.org

Title: Sustaining the AI Revolution: Transistor Scaling and Beyond

Speaker: Prof. Tsu-Jae King Liu

Abstract:

Advancements in semiconductor integrated circuit (IC) “chip” technology over the past 60+ years have enabled exponential growth in chip functionality with exponential reduction in cost per transistor, resulting in the proliferation of information and communication devices and systems, with revolutionary impact on society; today cloud computing, big data and artificial intelligence are driving the digital transformation of all industries. In this talk I will discuss three dimensions of IC technology advancement – transistor scaling, new computing architectures and new computing paradigms – to usher in the Age of Ambient Intelligence.

Speaker Bio:

Tsu-Jae King Liu earned her B.S., M.S. and Ph.D. degrees in electrical engineering at Stanford University in 1984, 1986 and 1994, respectively. From 1992 to 1996, she was member of research staff at the Xerox Palo Alto Research Center (PARC). In 1996, she joined the faculty of the Department of Electrical Engineering and Computer Sciences (EECS) at the University of California, Berkeley, where she is now Dean of the College of Engineering.

Liu is internationally known in academia and industry for her innovations in semiconductor devices and technology, and is highly regarded for her achievements as an instructor, mentor and administrator. She is a fellow of the Institute of Electrical and Electronics Engineers (IEEE), an elected member of the U.S. National Academy of Engineering, a fellow of the U.S. National Academy of Inventors, and Director of Intel Corporation and of Maxlinear, Inc. Her awards and honors include the Intel Outstanding Researcher in Nanotechnology Award, the IEEE Aldert van der Ziel Award for distinguished educational and research contributions to the field of electronic devices and materials, the IEEE Electron Devices Society Education Award, and the Defense Advanced Research Projects Agency (DARPA) Significant Technical Achievement Award for her role in the development of the FinFET, an advanced transistor design used in all high-end computer chips today.

=x=x=x=

Title: Semiconductors in Extreme Environments

Speaker: Prof. Debbie G. Senesky

Abstract:

Wide bandgap semiconductor materials such as silicon carbide (SiC), gallium nitride (GaN) and, diamond are well known for their inherent resilience to high-temperature and radiation-rich environments. This makes them attractive electronic platforms for use in space exploration and other extreme-environment applications (e.g., combustion, downhole, hypersonic aircraft). Gallium nitride (GaN) electronics have operated at temperatures as high as 1000°C making it a viable platform for robust space-grade (“tiny-but-tough”) electronics and nano-satellites. Even with this major technological breakthrough, there are still challenges in making GaN in low-cost formats with low defect density for proliferation in “beyond silicon” applications. New communities are adopting this electronic platform for a multitude of emerging device applications including the following: sensing, energy harvesting, actuation, and communication. In this talk, we will review and discuss the benefits of GaN’s two-dimensional electron gas (2DEG) over silicon’s p-n junction for space exploration applications (e.g., radiation-hardened, temperature-tolerant Venus probes). In addition, we will discuss the use of prolonged microgravity environments on the International Space Station (ISS) and commercial stations for future manufacturing of semiconductors for the benefit of life on Earth.

Speaker Bio:

Debbie G. Senesky is an Associate Professor at Stanford University in the Aeronautics and Astronautics Department and by courtesy, the Electrical Engineering Department. In addition, she is the Principal Investigator of the EXtreme Environment Microsystems Laboratory (XLab). Her research interests include the extreme-environment sensors, high-temperature electronics for Venus exploration, and nanomaterials synthesis within prolonged microgravity. She received the B.S. degree (2001) in mechanical engineering from the University of Southern California. She received the M.S. degree (2004) and Ph.D. degree (2007) in mechanical engineering from the University of California, Berkeley. She is currently serves as the Site Director for nano@stanford, as well as co-editor for the IEEE Journal of Microelectromechanical Systems (JMEMS) and Sensors (journal). In recognition of her work, she is a recipient of the Emerging Leader Abie Award from AnitaB.org, NASA Early Faculty Career Award, and Alfred P. Sloan Foundation Ph.D. Fellowship Award. More information about Prof. Senesky can be found at xlab.stanford.edu or on Instagram: @astrodebs.

=x=x=x=

Title: The Evolution of Analog Technology

Speaker: Lou N Hutter

Abstract:

Despite the major advancements made in semiconductor technology, the world remains a very analog place. Consequently, analog and power management integrated circuits are ubiquitous in almost every electronic system built today. Analog technology has made significant strides in the past 50+ years, migrating from low-density bipolar-based technologies and SSI products to highly scaled CMOS-based nodes and LSI and VLSI products today. The wide diversity of analog applications has driven a wide diversity of process technologies. This talk will discuss the evolution of analog technology from the 1970s to today and beyond, highlighting the many design constraints that have led to the diverse technology portfolio and rich component sets used today.

Speaker Bio:

Lou is a veteran of the semiconductor industry. He spent 29 years at Texas Instruments Inc., until retiring in 2007, as Director of TI’s Mixed-Signal Technology Development organization where he was responsible for worldwide analog, power, RF SiGe, and mixed-signal technology development, process delivery kits, production ramps, and transfers that supported every business unit in the company. He was elected a TI Fellow in 1995 based on his technical accomplishments and their revenue impact. In 2008, he joined Dongbu HiTek, in Seoul, S. Korea, as Senior Executive Vice President and General Manager of the newly created Analog Foundry Business Unit, where he was responsible for technology development, design enablement, IP development, and sales and marketing. During his tenure there, he increased revenues 4X, added many and significant new customers, and established Dongbu HiTek as a leading analog/power management foundry in the industry. Since 2012, he has been Principal of Lou Hutter Consulting LLC, advising foundries, IDMs, fabless companies, and material suppliers in the areas of analog and power technology, design infrastructure, organizational management, and business development. Lou has 47 U.S. patents, has published over 35 journal articles, has co-authored 1 book entitled Silicon Analog Components, now in its 2nd edition, and other book chapters. He has an MSEE from the Massachusetts Institute of Technology, and resides in Dallas, Texas.

======================================================================

Title: Gallium Nitride MMIC Power Amplifiers

for High Throughput Satellite (HTS) Applications (co-sponsored event with MTT-SCV)

Speaker: Jim Sowers

Wednesday, March 15, 2023

Registration Link: Here

Abstract:

There is a need for Solid State Power Amplifiers (SSPA’s) to be used in High Throughput Satellites (HTS) for commercial applications. Specifically when the amount of information passed through the transponders, i.e. capacity, is determined mainly by the quantity of beams the satellite can generate. This application is well suited for SSPA’s over the conventional TWTA solution as they are smaller and lighter weight enabling a simplification of HTS payload architectures, higher density physical integration, and the ability to support active array transmit solutions all of which increases the quantity of beams and thus capacity. More specifically, Gallium Nitride (GaN) Power Amplifiers (PA’s) have shown the ability to generate high RF output power levels with small size and high efficiency thereby enabling step function improvement in capacity. This paper will describe a 20GHz fully space qualified GaN PA module developed for KaBand commercial satellite downlinks. The design techniques, test results, and screening regimen required to meet the demanding performance and reliability requirements will be given. The result is a 20GHz module with >55dB of gain, >10W of Pout, >30% peak PAE, and NPR >15dB. To the authors knowledge this is the best fully space-qualified module performance at this frequency published to date.

Speaker Bio:

Jim has 40+ years of experience designing, developing, and manufacturing of RF, microwave, and millimeter-wave microelectronic components for satellite payloads as well as communication and radar systems for commercial and military use.

He is currently Payload Technical Partner for Unit Design Engieering and a Distinguished Engineer at Maxar Space Infrastructure. His responsibilities have encompassed the development of space-qualified, RF active, payload components from C-Band through V-Band including GaN Power Amplifiers, LNA’s, Receivers, Linearized Channel Amplifiers, Local Oscillators and MMICs. Additional responsibilities included Payload Manager for large Ku and Ka Band programs. Joining SS/L in June 1999, he was the Section Manager for Repeater Subsystems Electrical Engineering.

Preceding employent at SS/L, Mr. Sowers was with Lockheed Martin/Martin Marietta/GE Aerospace and was responsible for the research, design, and development of microwave and millimeter-wave MMICs and components for advanced radar and communications systems.

After graduating from Cornell University with a BSEE Jim joined Varian Associates where he was responsible for the research, design, and development of InP Gunn and IMPATT devices and circuits at V and W Bands. Receiving his Master of Science degree from Stanford University he subsequently took a position with Harris Microwave Semiconductor to develop RF/Microwave amplifiers for the military market.

Jim is a Life Senior Member of the IEEE, and has served on the Technical Program and Steering Committee of several IEEE conferences and is a past chair of the IEEE MTT Society -Santa Clara Valley Chapter. Additionally, he maintains an Adjunct Professor position at Santa Clara University.

===================================================================

Title: Atomistic Quantum Transport Modelling for Emergent 2D Material-based Device

Speaker: Dr. Youseung Lee

Friday, January 27, 2023 – 12:00PM – 1:00PM PDT

Registration Link: Here

Abstract:

Over the years, most of the manufactured electronic devices started to have at least one dimension in the nanometer scale. Concurrently, the non-equilibrium Green’s function (NEGF) framework has been broadly democratized to investigate quantum transport effects inside those devices. The latter framework has also proven its importance to correctly capture the underlining physics for the nano-scale devices. This talk will then discuss the latest development of atomistic quantum transport modelling for various emerging 2D materials-based devices. The first part of the talk will show an ab-initio approach that correctly captures the scattering mechanisms present in 2D FETs, combining the linearized Boltzmann Transport Equation (LBTE) and the NEGF formalism. Atomistic defect-variability study for 2D monolayer MoS2 FETs via many body defect-level corrections will also be presented. The second part will show the application of the ab-initio modeling framework to simulate Majorana transport, paving the way for topological qubits based on 2D nanoribbons. Atomistic modelling of van der Waals charge qubit manipulations and measurements in 2D materials will also be covered.

Speaker Bio:

Youseung Lee is a Post-doctoral Researcher at Nano-TCAD group of Integrated Systems Laboratory, ETH Zürich, Switzerland. He started his professional career as a TCAD engineer in Samsung Electronics Semiconductor Research Center, Korea in 2010 after he obtained MSc from KAIST. At Samsung, he worked on the development of 20, 14, and 10 nm logic technology nodes through TCAD process/device simulations. After the industrial career, he joined IM2NP-CNRS (Institut Matériaux Microélectronique Nanosciences de Provence) National Laboratory, France for PhD. Currently his main research focuses on the development of physics models dedicated to nano-electronic devices, along three main pillars: (A) computationally efficient quantum transport methods, (B) many body physics modelling, and (C) atomistic modelling for quantum computing devices hosting qubits.

===================================================================

Co-sponsored Event with SF Bay Area PELS Chapter

Title: Wide Bandgap Semiconductors: Opportunities and Challenges for Improved Modeling and Characterization Methods in Power Electronic Applications

Speaker: Prof. Raghav Khanna

Thursday, January 26, 2023 at 6:30PM – 8:00PM PDT

Abstract:

Wide bandgap semiconductor devices based on gallium nitride (GaN) and silicon carbide (SiC) offer myriads of advantages over traditional silicon (Si)-based devices for applications in power electronics. These advantages include, among others, faster switching capabilities, allowing for reduced filtering components within converter topologies, thus leading to improved power density. Despite their many advantages, several challenges related to technological readiness level have hindered the widespread adoption of these devices. At the device-physics level, for example, the theoretical high voltage capability of GaN has yet to be commercially realized. At the device-circuits level, the fast-switching capability of SiC, though generally a beneficial attribute, has led to undesirable injected harmonic content into power electronic converters, leading to detrimental circuit-behavior. For these reasons, advanced modeling, and characterization methods for both GaN and SiC are needed, so that these devices can realize their full performance entitlement.

This talk will present a broad array of modeling and characterization methodologies for GaN and SiC semiconductors. Device physics simulations using finite element modeling techniques will be presented, demonstrating the high voltage capability of vertical GaN diodes. It will be shown how these types of models can lead to the design and fabrication of future high voltage and reliable vertical GaN devices. Analytical physics-based models of GaN diodes, based on first principles, will also be presented. For these types of models, tradeoffs between model-fidelity and convergence-time in circuit-simulations will be discussed. Behavioral models of SiC MOSFETs, based on mathematical curve-fitted equations, will then be presented. These models will demonstrate the need to capture the frequency-dependence of the device’s parasitic per-terminal junction capacitances, as well as that of the parasitic package inductances, in order to construct a comprehensive empirically validated high-fidelity circuit-simulation. New strategies that can enable the development of hybrid-physics and -behavioral models will be presented, in a manner that offers utility to both device fabrication engineers, as well as application-circuit designers. For the various types of models presented, the importance of the interplay and refinement between simulation and empirical validation will be emphasized. This talk will conclude with characterization techniques and opportunities for wide bandgap semiconductors in space. The work presented in this talk lends itself well to developing strategies for multilevel integrated modeling infrastructures of next generation GaN and SiC devices, and to aid in the design, fabrication, and implementation of future high-voltage and reliable wide and ultrawide bandgap semiconductors.

Speaker Bio:

Raghav Khanna received the B.S. degree, M.S. degree, and Ph.D. degree in electrical engineering from the University of Pittsburgh, Pittsburgh, PA, USA in 2007, 2010, and 2014, respectively. Raghav has worked for several industries including Lockheed Martin (Philadelphia, PA), PPG Industries (Pittsburgh, PA) and HRL Laboratories (Malibu CA). At HRL, he was directly involved with the development of GaN based battery chargers for electric vehicles. In 2015, he joined the electrical engineering and computer science department at The University of Toledo. He is currently an Associate Professor and holds the position of Leidich Family Endowed Professor in Power and Energy Systems. His research interests are in characterization and modeling of wide bandgap semiconductors for applications in next generation power electronics, including; renewable energy, electric vehicles, aerospace and maritime systems, and in low power consumer electronics. He is also conducting extensive research on control strategies for integration of distributed energy resources. He recently received grants from the U.S. Department of Defense, U.S. Department of Energy, and NASA Jet Propulsion Laboratory to further develop his research activities.

===================================================================

IEEE-EDS September Seminar (Webex only)

Title: Design and Modelling Challenges for Very Large-Scale Integrated Quantum Processors in Foundry CMOS Technologies

Speaker: Sorin P. Voinigescu

Friday, November 18th, 2022 at noon – 1PM PDT

Webex link will be distributed to the registrant via email.

Organizer contact: Hiu Yung Wong (hiuyung.wong at sjsu.edu)

Abstract:

This presentation will discuss the main challenges in the physical implementation, design, hierarchical modelling and simulation of the scalable qubit array and of the cryogenic control and readout electronics for future Quantum Processors with millions of qubits manufactured in commercial FDSOI and FinFET foundry technologies. Impact of process manufacturing rules restrictions and process variation on qubit design and modelling, circuit heat dissipation and layout miniaturization to fit the qubit array pitch, qubit-to-qubit crosstalk, and the need for atomistic, classical, and behavioural qubit simulation and modelling will be covered in detail.

Speaker Bio:

Sorin P. Voinigescu is a Professor in the Electrical and Computer Engineering Department at the University of Toronto where he holds the Stanley Ho Chair in Microelectronics and is the Director of the VLSI Research Group. He is an IEEE Fellow and an expert on millimeter-wave and 100+Gb/s integrated circuits and atomic-scale semiconductor device technologies. He obtained his PhD degree in Electrical and Computer Engineering from the University of Toronto in 1994 and his M.Sc. Degree in Electronics and Telecommunications from the Politechnical Institute of Bucharest in 1984.

———————————————————————-

Title: The LLNL Quantum Design and Integration Testbed

Speaker: Dr. Yaniv Jacob Rosen

Friday, September 2, 2022 at noon – 1PM PDT

Webex link will be distributed to the registrant via email.

Organizer contact: Hiu Yung Wong (hiuyung.wong at sjsu.edu)

Abstract:

Quantum science and technology is a focal point of research at LLNL. To that end we are developing QuDIT, a quantum testbed that allows us to explore different methods of implementing quantum computing and sensing. In this presentation we will introduce the basics of quantum computing and how they achieve a speedup in computation. We will explore LLNL’s implementation which uses the higher levels of the quantum elements to increase the computational space. Despite adding computational complexity, using Qudits instead of Qubits simplifies the hardware and can improve performance for certain calculations. We will show example simulation pulses developed using optimal control techniques designed to solve quantum systems, and discuss the sources of noise and decoherence that affect our system. This presentation will attempt to give a broad overview of the RF engineering, the material science, and the classical computer science that goes into developing the LLNL testbed.

Speaker Bio:

Dr. Yaniv is the deputy group leader of the Quantum Coherent Device Physics group. He works on noise in superconducting devices with an emphasis on two-level-system dielectric loss. Yaniv graduated with a B.A. in physics and applied mathematics from the University of California (UC), Berkeley in 2006. He received his Ph.D. in condensed matter physics under Ivan Schuller at UC San Diego in 2013, where he studied thin-film superconductivity under the influence of nano-magnetic dots. From there he engaged in postdoctoral study at the Laboratory for Physical Sciences with Kevin Osborn, studying two-level systems in dielectrics. In 2016, he joined the Lawrence Livermore team where he helped bring online the LLNL Quantum design and Integration Testbed.

Title: Memristive Neuromorphic Computing Beyond Moore’s Law

Speaker: Prof. Sung-Mo “Steve” Kang, UC Santa Cruz

Friday, November 12, 2021 at noon – 1PM PDT

Webex link will be distributed to the registrant via email.

Organizer contact: Jin-Woo Han (jin-woo.han at nasa.gov)

Abstract:

Neuromorphic computing is pursued to overcome the limitations of von Neumann architecture and Moore’s law. Harnessing brain-inspired properties such as in-memory computing, spike-based encoding, and adaptation has demonstrably shown to bolster energy-delay efficiency by a few orders of magnitude classes of computation. The use of functional building blocks in integrated circuits that exhibit characteristics like the biological building blocks of the central nervous system is expected to enable circuits to mimic tasks associated with human cognition and sensory perception. Thus, a variety of approaches has been used to design electronic neurons that generate spiking signals and to implement synaptic interconnects. The memristor was introduced by Leon Chua in 1971 as a circuit element that is as fundamental as R, L, and C. The notion of the memristor was generalized by Chua and Kang in 1976. The research and development of memristor circuits and systems were propelled by the nanoscale memristors fabricated by Williams et al. in 2008. Since then, a myriad of applications has been developed for memristors in storage-class memory, sensing, logic operations and memcomputing. Recently, memristors have become available through commercial fabrication processes and are commercially used in non-volatile resistive random-access memories (RRAM). Memristor technologies have ushered in new approaches for emulating both biological neurons and synapses. Synaptic plasticity has been demonstrated in memristors by using spike trains to increase (potentiate) or decrease (depress) the memristor’s conductance. In this talk, we will discuss the roles of memristors in designing new building blocks for memristive neural networks for hardware acceleration. How to design new memristive neurons and synapses for neuromorphic computation will be discussed in view of integration packing density, power consumption, and physical layout of neuronal networks. It is projected that at the 3.5 nm memristor technology node, memristive neurons and synapses in mimicry of human brain can be densely integrated in a 2400 〖cm〗^2 of surface area with a total power consumption in the ballpark of 20W.

Speaker Bio:

Sung-Mo “Steve” Kang is a Distinguished Chair Professor of the Jack Baskin School of Engineering, UC Santa Cruz, and Chancellor Emeritus of UC Merced and President Emeritus of KAIST. He returned to academia in 1985 from industry to join the faculty of the University of Illinois at Urbana-Champaign. Until then, he had led the development of world’s premier CMOS 32-bit VLSI microprocessor chipsets for telecommunication and computing applications as a technical supervisor of AT&T Bell laboratories, Murray Hill, NJ. From 1995 to 2000, he served as Department Head of ECE at the University of Illinois at Urbana-Champaign and became a Dean of Engineering at UC Santa Cruz. He has received honors, including the Silicon Valley Engineering Hall of Fame induction, Alexander von Humboldt Senior US Scientists Award, IEEE Millennium Medal, IEEE Mac Van Valkenburg Circuits and Systems (CAS) Society Award, IEEE CAS Technical Excellence Award, the US Semiconductor Research Corporation (SRC) Technical Excellence Award, IEEE Graduate Teaching Technical Field Award, IEEE CAS John Choma Education Award, Chang-Lin Tien Education Leadership Award, and distinguished alumnus awards from UC Berkeley, The University at Buffalo, Fairleigh Dickinson University, and Yonsei University. He received his B.S. degree from Fairleigh Dickinson University, Teaneck, New Jersey in 1970, M.S. degree from the State University of New York at Buffalo in 1972, and Ph.D. degree from UC Berkeley in 1975. He holds 16 U.S. patents, published over 500 papers, and 10 books. Dr. Kang is a Fellow of the IEEE, the Association for Computing Machinery (ACM), and the American Association for the Advancement of Science (AAAS). He is a member of Korean Academy of Science and Technology and a foreign member of National Academy of Engineering, Korea. His research interest includes modeling and simulation of semiconductor devices, memristors and memristive systems, low-power VLSI circuit design, nano-bioelectronic circuits, and neuromorphic computing.

Title: TCAD/SPICE-Augmented Machine Learning for Defect and Variation Study

Speaker: Dr. Hiu Yung Wong, San Jose State University

Friday, October 15, 2021 at noon – 1PM PDT

Webex link will be distributed to the registrant via email.

Organizer contact: John Choi (wonhochoi at micron.com)

Abstract:

In semiconductor technology development, it is desirable to pinpoint the source of defect or variation through electrical measurements, which are non-destructive and have much higher throughput than the traditional failure analysis. This can be achieved through machine learning which is a powerful tool for correlating the electrical characteristics to the nature of the defect/variation. However, a good machine is only possible with enough well-controlled training data, which is difficult to obtain experimentally. TCAD and SPICE simulations which are well-calibrated to experimental data are proposed to generate the training data.

In this talk, we will first demonstrate the use of TCAD to generate data to train machines to deduce the epitaxial layer thickness of Si p-i-n diodes and the workfunction and operating temperature variation of Ga2O3 Schottky Barrier Diodes, based solely on the measured electrical characteristics. We will emphasize the use of minimal domain expertise to obviate the difficulties in feature extraction. We will also demonstrate the techniques that are important to make the TCAD-trained machine applicable to predicting experimental data. SPICE-augmented ML will be demonstrated for detecting contact resistance degradation in inverters. Finally, we will discuss the use of TCAD-augmented machines to help reverse engineering and understand novel devices.

Speaker Bio:

Hiu Yung Wong is an Assistant Professor in the EE department, San Jose State University. He received his Ph.D. degree in Electrical Engineering and Computer Science from the University of California, Berkeley in 2006. From 2006 to 2009, he worked as a Technology Integration Engineer in Spansion. From 2009 to 2018, he was a TCAD Senior Staff Application Engineer in Synopsys, during which he received Synopsys Excellence Award in 2010. In 2021, he received the NSF CAREER award and the Newnan Brothers Award for Faculty Excellence.

His research interests include the applications of machine learning in simulation and manufacturing, cryogenic electronics, quantum computing, reliability simulations, wide bandgap devices (such as GaN, SiC, Ga2O3, and diamond) simulations, novel semiconductor devices design, and Design Technology Co-Optimization (DTCO). His work has produced 80 papers and 10 issued patents.

IEEE-EDS April Seminar Series (Webex only)

Title: An Addiction to Low Cost Per Memory Bit – How to Recognize it and What to Do About it

Speaker: Dr. Andy Walker, Spin Memory inc.

Friday, April 23, 2021 at noon – 1PM PDT

Abstract:

The phenomenal rise in the amounts of data has put great pressure on the semiconductor industry to provide low cost memory solutions. The result is a constant drive to lower the cost per bit of DRAM, SRAM and NAND Flash. In addition, AI requires intense store and recall between processor and memory. In the rush to provide low cost solutions, other attributes have been treated as expendable as an acceptable cost of doing business. Several examples come to mind: short product lifetimes because of limited NAND Flash endurance; data insecurity because of DRAM Rowhammer; poor energy efficiency because of the need to bring growing amounts of data from DRAM into the processor chip due to SRAM area inefficiencies. All such “negative externalities” have a cost that is not included in the product cost but affects society in terms of wasted energy and resources. This talk looks into their origins and consequences and is a call to action for a more comprehensive understanding of what cost per bit really means.

Speaker Bio:

Andy Walker has been working in silicon technology since 1985. After a BSc in physics from Dundee University in Scotland he joined Philips Research Laboratory in Eindhoven, The Netherlands. His PhD from the Technical University of Eindhoven arose from his research work at Philips. In 1994 he came to Silicon Valley and worked at various companies including Cypress, Matrix and Spin Memory. He also founded Schiltron Corporation to develop new forms of monolithic memories. He has been fortunate in being able to work in many interesting areas of silicon devices and process technology including MOS device physics, nonvolatile memories, ESD and Latch-up, TFTs and MRAM.

IEEE-EDS January Seminar Series (Webex only)

Title: Compute-in-Memory with Emerging Nonvolatile-Memories: Challenges and Prospects

Speaker: Prof. Shimeng Yu, Georgia Institute of Technology

Friday, January 15, 2021 at noon – 1PM PDT

Abstract:

Compute-in-memory (CIM) is a new computing paradigm that addresses the memory-wall problem in the deep learning accelerator. In this presentation, first I will present our DNN+NeuroSim benchmark framework that is interfaced with Tensorflow/PyTorch to evaluate different device technologies for state-of-the-art DNN models. We will discuss about the pros and cons of various non-volatile memory candidates and the most important device specifications for inference/training, respectively. Second, I will present our RRAM-CIM prototype chips that are integrated with CMOS peripheral circuitry and its performance. Furthermore, we will show our experimental characterizations of the multilevel RRAM’s variability and reliability and their impact on DNN inference accuracy. To overcome the challenges of the RRAM-CIM prototypes we identified, we propose monolithic 3D integration with back-end-of-line (BEOL) transistors as a potential solution.

Speaker Bio:

Shimeng Yu is an associate professor of electrical and computer engineering at the Georgia Institute of Technology. He received the B.S. degree in microelectronics from Peking University in 2009, and the M.S. degree and Ph.D. degree in electrical engineering from Stanford University in 2011 and 2013, respectively. From 2013 to 2018, he was an assistant professor at Arizona State University. Prof. Yu’s research interests are nanoelectronic devices and circuits for energy-efficient computing systems. His expertise is on the emerging non-volatile memories (e.g., RRAM, ferroelectrics) for different applications such as deep learning accelerator, neuromorphic computing, monolithic 3D integration, and hardware security. Among Prof. Yu’s honors, he was a recipient of the NSF Faculty Early CAREER Award in 2016, the IEEE Electron Devices Society (EDS) Early Career Award in 2017, the ACM Special Interests Group on Design Automation (SIGDA) Outstanding New Faculty Award in 2018, the Semiconductor Research Corporation (SRC) Young Faculty Award in 2019, and the ACM/IEEE Design Automation Conference (DAC) Under-40 Innovators Award in 2020, etc. Prof. Yu is active in professional services. He served or is serving many premier conferences as technical program committee, including IEEE International Electron Devices Meeting (IEDM), IEEE Symposium on VLSI Technology, etc. He is a senior member of the IEEE..

************************************************************************************

IEEE-EDS October Seminar Series (Webex only)

Title: Coupled Oscillator based Computing: Using Nature to Solve Difficult Problems

Speaker: Prof. Chris H. Kim, University of Minnesota

Friday, October 30, 2020 at 11AM – noon PDT

Abstract:

In this talk, I will introduce a first-of-its kind quantum-inspired coupled oscillator based compute engine implemented in a standard 65nm technology targeted for NP-hard or NP-complete problems such as max-cut, graph coloring, traveling salesman, and pattern recognition. The NP-hard problem is first mapped to the coupling weights while the solution is represented by the phases of the individual oscillators, which are read out using on-chip phase sampling circuits. Our hardware exploits the natural tendency of a network of coupled oscillator to settle to the ground state, which offers significant performance and power advantages compared to traditional digital approaches.

Speaker Bio:

Chris H. Kim received his B.S. and M.S. degrees from Seoul National University and a Ph.D. degree from Purdue University. He is currently a professor at the University of Minnesota. Prof. Kim is the recipient of the University of Minnesota Taylor Award for Distinguished Research, SRC Technical Excellence Award, Council of Graduate Students Outstanding Faculty Award, NSF CAREER Award, Mcknight Foundation Land-Grant Professorship, 3M Non-Tenured Faculty Award, DAC/ISSCC Student Design Contest Award, IBM Faculty Partnership Award, IEEE Circuits and Systems Society Outstanding Young Author Award, the ICCAD Ten Year Retrospective Most Influential Paper Award, ISLPED Low Power Design Contest Award (4 times), and ISLPED Best Paper Award (2 times). His group has expertise in digital, mixed-signal, and memory IC design, with special emphasis on circuit reliability, hardware security, memory circuits, radiation effects, time-based circuits, beyond-CMOS technologies, and machine learning hardware design. He is an IEEE fellow.

************************************************************************************

Title: Memory Errors in Production Systems – Insights from the Field

Speaker: Dr. Sudhanva Gurumurthi, Principal Member of Technical Staff, AMD

Friday, August 28, 2020 at 12PM – 1PM PDT

Abstract:

Memory reliability is important for the correct operation of computing systems. While technology scaling as paved the way for improvements in the capacity and energy-efficiency of memory, the reliability aspects of such scaling must be well characterized and addressed in the design of computer hardware. AMD has collected and analyzed memory reliability data from several production systems running in data centers. This data spans several generations of DRAM technologies, as well as SRAM. This talk will first explain how bit-cell reliability can impact on the design and use of computing hardware and highlight the importance of studying memory faults from commercial hardware in the field. The talk will then present memory reliability data and insights from AMD’s field studies and discuss their implications from the viewpoint architecting resilient systems.

Speaker Bio:

Sudhanva Gurumurthi is a Principal Member of the Technical Staff at AMD, where he leads advanced development in Reliability, Availability, and Serviceability (RAS). He used to be an Associate Professor with tenure in the Computer Science Department at the University of Virginia. Sudhanva is a recipient of the NSF CAREER Award, a Google Focused Research Award, two Google Faculty Research Awards, and other NSF and industry awards. He is a Senior Member of the IEEE and the ACM.

************************************************************************************

IEEE-EDS July Distinguished Lecture: Differentiated Fully Depleted SOI (FDSOI) Technology for Highly Efficient and Integrated mmWave Wireless Connectivity Solution (Webex Only)

Speaker: Dr. Anirban Bandyopadhyay, Director, Strategic Marketing and Business Analytics, GLOBALFOUNDRIES, Inc., Santa Clara, CA

Friday, July 24, 2020 at 12PM – 1PM PDT

Abstract:

The emergence of enhanced mobile broadband (eMBB) connectivity based on mmWave 5G and the emerging prospect of broadband internet to using non-terrestrial mmwave backhaul using low earth orbit (LEO) satellite generated huge interest in the entire telecommunication ecosystem. While mmwave allows huge bandwidth of channels to enable enhanced broadband, it also poses a lot of technical challenges in terms of coverage, generating enough transmitted power efficiently particularly in the uplink, system cost & scaling and long term reliability of the hardware system particularly for infrastructure including Satellite born systems. Current talk will focus on how Silicon technologies based on differentiated fully depleted SOI (FDSOI) can address the above challenges by enabling a highly efficient and integrated radio without compromising on the mmWave performance and reliability. Talk will highlight the technology Figures of Merits (FOMs) for a mmwave phased array system and how a differentiated FDSOI technology platform compares with other silicon technologies in terms of devices and circuits.

Speaker Bio:

Dr. Anirban Bandyopadhyay is the Director, Strategic Marketing and Business Analytics within the Mobility & Wireless Infrastructure Business Unit of GLOBALFOUNDRIES, USA. His work is currently focused on hardware architecture & technology evaluations for emerging RF and mmWave applications. Prior to joining GLOBALFOUNDRIES, he was with IBM Microelectronics, New York and with Intel, California where he worked on different areas like RF Design Enablement, Silicon Photonics, signal integrity in RF & Mixed signal SOC’s. Dr. Bandyopadhyay did his PhD in Electrical Engineering from Tata Institute of Fundamental Research, India and Post-Doctoral research at Nortel, Canada and at Oregon State University, USA. He represents Global Foundries in different industry consortia on RF/mmWave applications and is a Distinguished Lecturer of IEEE Electron Devices Society.

************************************************************************************

IEEE-EDS June Seminar: (Ultra-) Wide-Bandgap Devices: Reshaping the Power Electronics Landscape (Webex Only)

Speaker: Dr. Yuhao Zhang, Assistant Professor, Center for Power Electronics Systems, Virginia Tech

Friday, June 12, 2020 at 12PM – 1PM PDT

View Presentation

Abstract:

Power electronics is the application of solid-state electronics for the control and processing of electrical energy. It is used ubiquitously in consumer electronics, electric vehicles, data centers, renewable energy systems, and smart grid. The power semiconductor device, as the cornerstone technology in power electronics, is key to improving the efficiency, cost and form factor of power electronic systems.

Recently, the power electronics landscape has been significantly reshaped with the production and application of power devices based on wide-bandgap (WBG) semiconductors, such as gallium nitride (GaN) and silicon carbide (SiC). Besides advancing the performance of traditional power systems, WBG devices have also enabled many emerging applications that are beyond the realm of silicon (Si) as well as changed the manufacturing paradigm of power electronics. On the horizon is the power devices based on ultra-wide-bandgap (UWBG) materials, which promises superior performance over GaN and SiC and is at the relatively early stage of research development.

This talk will provide a comprehensive overview of major WBG and UWBG power device technologies, spanning materials, devices, reliability and applications. Some research projects in the PI’s group in collaboration with industry will also be introduced.

Speaker Bio:

Dr. Yuhao Zhang is an assistant professor in the Center for Power Electronics Systems (CPES) at Virginia Tech. Before joining CPES, he worked as a postdoctoral associate at Massachusetts Institute of Technology (MIT) from 2017 to 2018. He received his Ph. D. and S. M., both in electrical engineering from MIT in 2017 and 2013, respectively. Prior to joining MIT, he received his B. S. in physics from Peking University in 2011 with the highest honor. He received the MIT Microsystems Technology Laboratories Doctoral Dissertation Award in Spring 2017, for his impactful work on vertical GaN power devices.

His research interest is at the intersection of power electronics, micro/nano-electronic devices and advanced semiconductor materials. His group is currently working on the development of novel WBG and UWBG power devices, reliability and robustness of emerging power devices, and ultra-wide bandgap power semiconductors.

Center for Power Electronics Systems (CPES) (https://cpes.vt.edu/) at Virginia Tech is one of the largest university research center in power electronics. For the past two decades, CPES has a worldwide reputation for its research advances, its work with industry to improve the entire field, and its many talented graduates. The CPES industry consortium comprises over 80 member companies engaged with CPES to stay abreast of technological developments in power electronics.

************************************************************************************

IEEE-EDS March Seminar: Wide Bandgap Devices Enabling High Power and High Frequency Electronics (Webex Only)

Speaker: Professor Srabanti Chowdhury, Stanford University

Friday, March 13, 2020 at 11:45AM – 1PM

Abstract:

We live in extremely exciting times, often identified as the age of the fourth industrial revolution. With electrification at every level, we are witnessing the most significant transformation of transportation since the internal combustion engine. Renewable energy is now a reality. IoT with the ever-expanding need for sensors and low power electronics is changing our lives dramatically. Robotics and autonomous vehicles are upon us. Both new and existing applications are demanding physical electronics solutions with new materials, devices and heterogeneous integration to drive these innovations to their full potential.

Wide-bandgap (WBG) semiconductors present a pathway to enable much of these electronics with higher efficiency and newer functionalities. Semiconductor devices with higher power density have unprecedented value in both power and high frequency electronics. Reducing conversion losses is not only critical for minimizing consumption of limited resources, it simultaneously enables new compact and reduced weight solutions, the basis for a new industry offering increased power conversion performance at reduced system cost. Equally importantly, GaN has opened the door to other ultra-wide bandgap materials such as Diamond, Aluminum Nitride and Gallium Oxide.

Speaker Bio:

Srabanti Chowdhury (George and Ida Mary Hoover faculty fellow, Gabilan fellow) is an associate professor of Electrical Engineering (EE) at Stanford. She received her masters and PhD in Electrical engineering from UCSB in 2008 and 2010 respectively. Her research focuses on wideband gap (WBG) materials and device engineering for energy efficient and compact system architecture for power electronics, and RF applications. Besides Gallium Nitride, her group is exploring Diamond for various electronic applications. She received the DARPA Young Faculty Award, NSF CAREER and AFOSR Young Investigator Program (YIP) in 2015. In 2016 she received the Young Scientist award at the International Symposium on Compound Semiconductors (ISCS). She became a senior member of IEEE in 2017, and NAE Frontiers of Engineering Alumni in 2019. She has been named as a Sloan Research Fellow in 2020 in Physics for her research contribution.

Among her various synergistic activities, she serves as the member of two committees under IEEE Electron Device Society (Compound Semiconductor Devices & Circuits Committee Members and Power Devices and ICs Committee). She has served the IEEE International Electron Devices Meeting (IEDM) technical subcommittee on Power Devices & Compound Semiconductor and High-Speed Devices (PC) sub-committee in 2016 and 2017. She was the PC subcommittee chair for IEDM-2018 and continues to serve the IEDM executive committee. Her work has produced over 80 journal papers, 100 conference presentations, and 20 issued patents.

************************************************************************************