#### **IBM Research**

#### Nanotechnology Trends in Nonvolatile Memory Devices

**Gian-Luca Bona**

gianni@us.ibm.com IBM Research, Almaden Research Center

© 2008 IBM Corporation

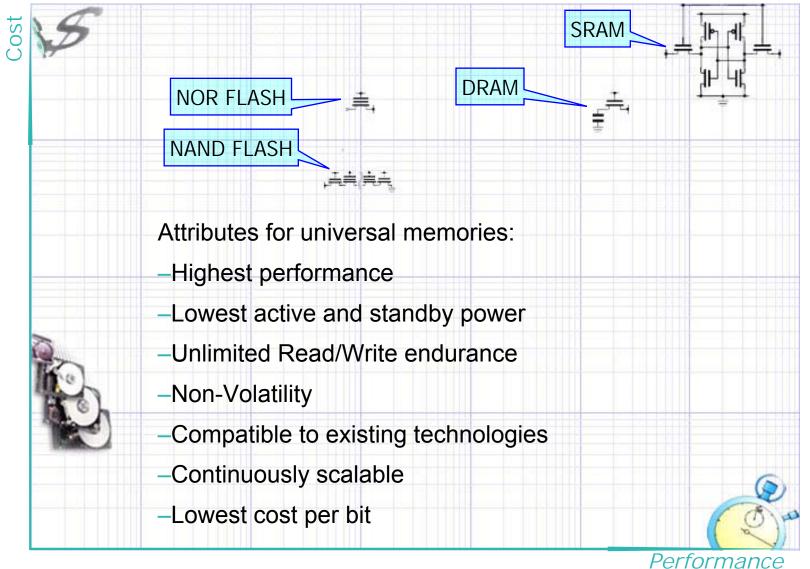

# The Elusive Universal Memory

#### EE Times: Semi News 'Universal' memory market to hit \$75 billion in 2019, says iSuppli

#### Peter Clarke (07/27/2005 7:45 AM EDT) URL: <u>http://www.eetimes.com/showArticle.jhtml?articleID=166402857</u>

LONDON - The market for a memory integrated circuit that combines the speed of SRAM, the density of DRAM and the non-volatility of flash, could be \$76.3 billion by 2019, according to market research company iSuppli Corp. (El Segundo, Calif.).

The so-called "universal" memory would, by then, have grabbed about 80 percent of the market, the market researcher has estimated in a long-range forecast it described as "speculative."

There is no single semiconductor memory technology today that has all the desired attributes, which on top of speed, density and non-volatility include: low-cost of manufacture, low switching energy and scalability to nanometer-scale dimension.

Products in various stages of commercialization that include at least some of the attributes include: Ovonic Unified Memory (OUM), Magneto-Resistive RAM (MRAM), Ferroelectric RAM (FRAM) and Nanotube RAM (NRAM), iSuppli said. But the rewards for a winning technology are likely to be immense with the memory market set to double from \$46.8 billion posted in 2004 to \$95.4 billion by 2019, iSuppli said.

The market researcher said that it does not usually forecast markets beyond a five-year horizon. However, due to the emerging status of the universal memory market, a longer-range forecast is required.

All material on this site <u>Copyright © 2005 CMP Media LLC</u>. All rights reserved. <u>Privacy Statement</u> | <u>Your California Privacy Rights</u> | <u>Terms of Service</u>

# **Incumbent Semiconductor Memories**

|   | _ | - |     |   |

|---|---|---|-----|---|

|   | - |   | _   |   |

|   |   |   | 1.1 |   |

| - | - |   | -   | - |

|   |   |   |     |   |

|   |   |   |     |   |

## **Incumbent Semiconductor Memories**

© 2008 IBM Corporation

IBM

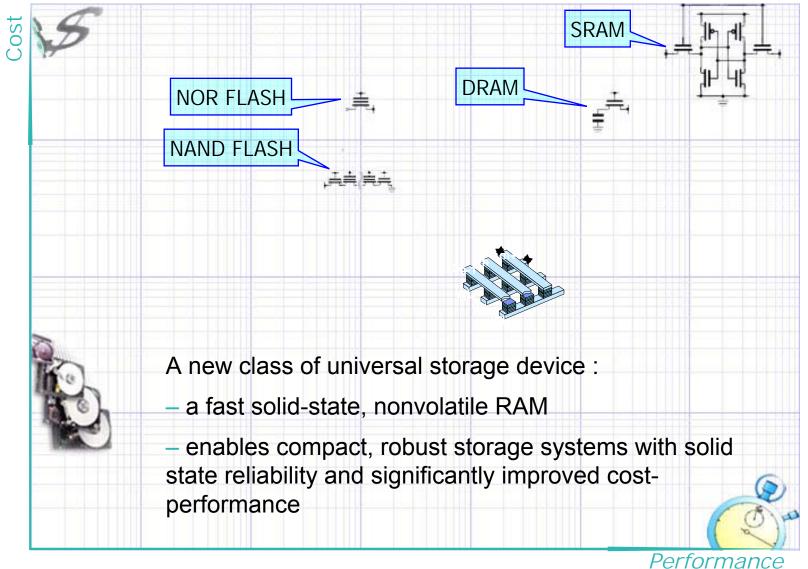

## Non-volatile, universal semiconductor memory

- Everyone is looking for a dense (cheap) crosspoint memory.

- It is relatively easy to identify materials that show bistable hysteretic behavior (easily distinguishable, stable on/off states).

| CONTRACTOR OF | JEL. | A COMPANY |     |                                  |

|---------------|------|-----------|-----|----------------------------------|

| IBM           |      | 000       | roh |                                  |

|               | Re   | Sea       |     | a da da fata da se               |

|               |      |           |     | and in the set of the set of the |

|   |   | 1.1 | _ | _ |

|---|---|-----|---|---|

| - | - | -   |   | = |

|   |   | =   |   |   |

| _ | _ |     |   |   |

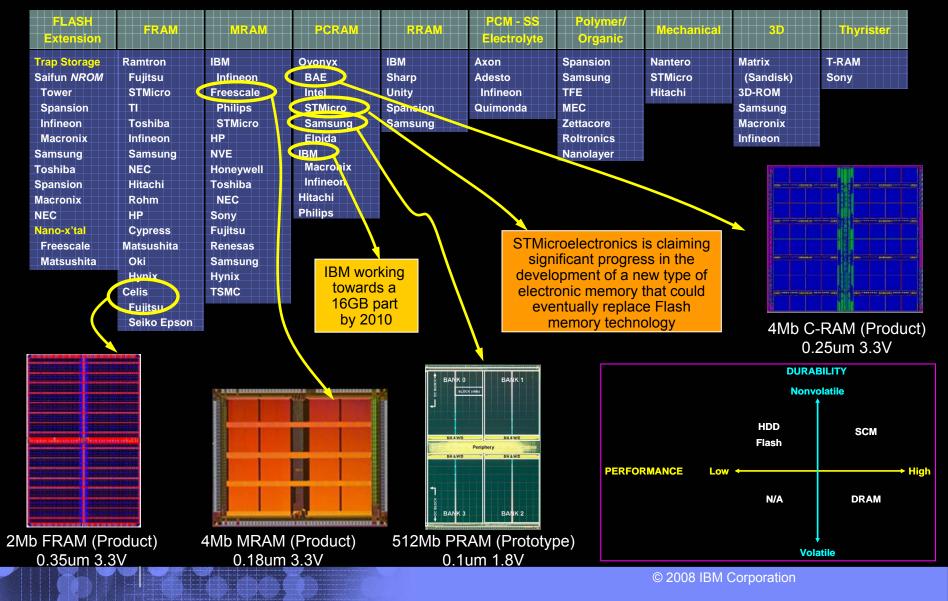

## The Memory Landscape

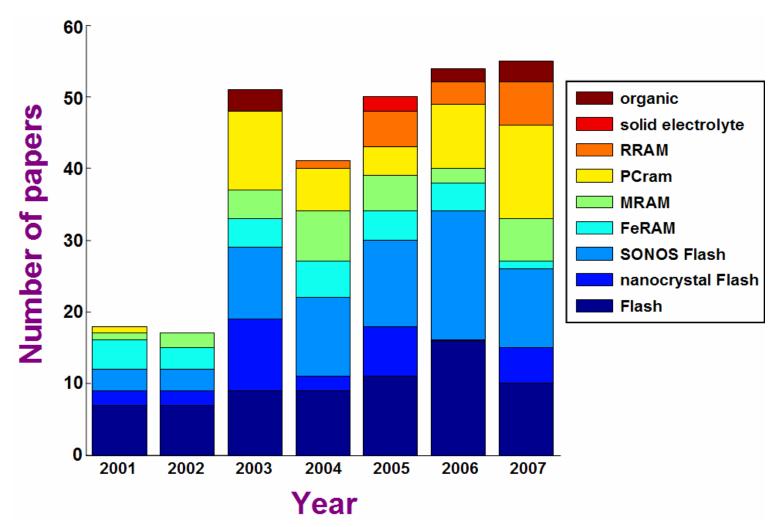

# **Histogram of Memory Papers**

Papers presented at Symposium on VLSI Technology and IEDM; Ref.: G. Burr et al., IBM Journal of R&D, Vol.52, No.4/5, July 2008

# **Emerging Memory Technologies**

**IBM Research**

#### Memory technology remains an active focus area for the industry

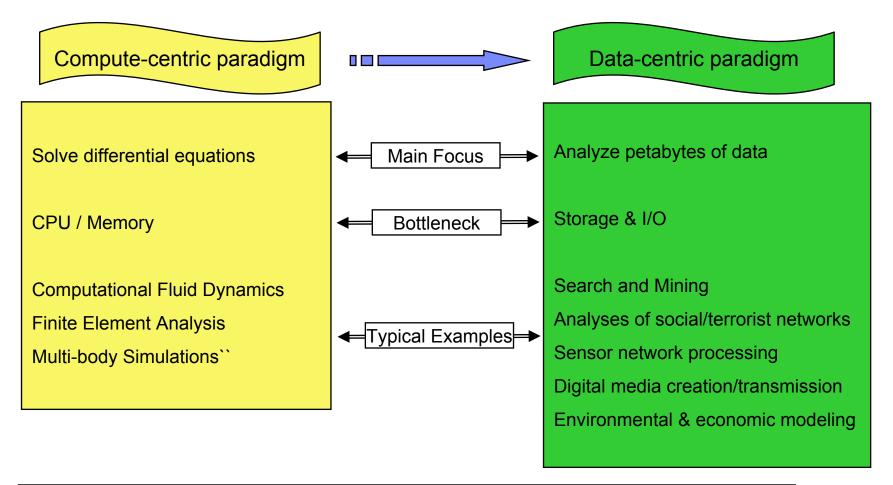

#### Critical applications are undergoing a paradigm shift

Thesis: Disks or Flash can't keep up w/data centric applications

Proposal: Develop device technology and build a high density array and demonstrate performance and endurance for the data-centric paradigm

© 2008 IBM Corporation

# What are the limitations with disks?

- Bandwidth Access Time Reliability Power

- Disk Performance improves very slowly

- Gap between processor and disk performance widens rapidly

- Bandwidth 100MB/s slow improvement

- gap can be solved with many parallel disks

- but need 10,000 disks today, >1,000,000 disks by 2020

- but that's just for a traditional high-end HPC system

- data intensive problems are much worse

- Access time gap has no good solution

- disk access times (msec); decrease only 5% per year

- complex caching or task switching schemes help sometimes

- Disk <u>power dissipation</u> is a major factor in data-centric systems (~4W/disk)

- Newest disk generations are less reliable than older ones

- Data losses occur in even the best enterprise-class storage systems

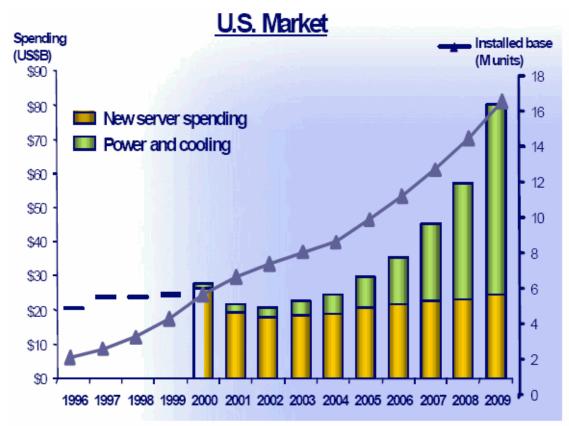

# Power & space in the server room

The cache/memory/storage hierarchy is rapidly becoming the bottleneck for large systems.

We know how to create MIPS & MFLOPS cheaply and in abundance,

#### but feeding them with data has become

the performance-limiting and most-expensive part of a system (in **both \$ and Watts**).

Extrapolation to 2020 (at 90% CGR  $\rightarrow$  need

• 25 <u>Mega</u>watts

R. Freitas and W. Wilcke, *Storage Class Memory: the next storage system technology* –to appear in "Storage Technologies & Systems" special issue of the IBM Journal of R&D.

| - |   |       |

|---|---|-------|

|   | - |       |

|   |   |       |

|   | _ |       |

|   |   | = 7 = |

# What are the limitations with Flash?

- Read/Write Access Times Write endurance Block architecture

- Flash Performance showing no improvement

- Gap between processor and Flash performance continues to widen

- Write endurance  $<10^6$  and showing no improvement trends

- Need >10<sup>9</sup> to cater to frequent writes as data continually flows into the system

- Tomorrow's hand-held devices will be continuously updated

- Intel applications characterized by continuous data streams

- Access time gap has no good solution

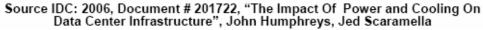

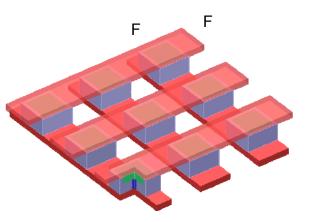

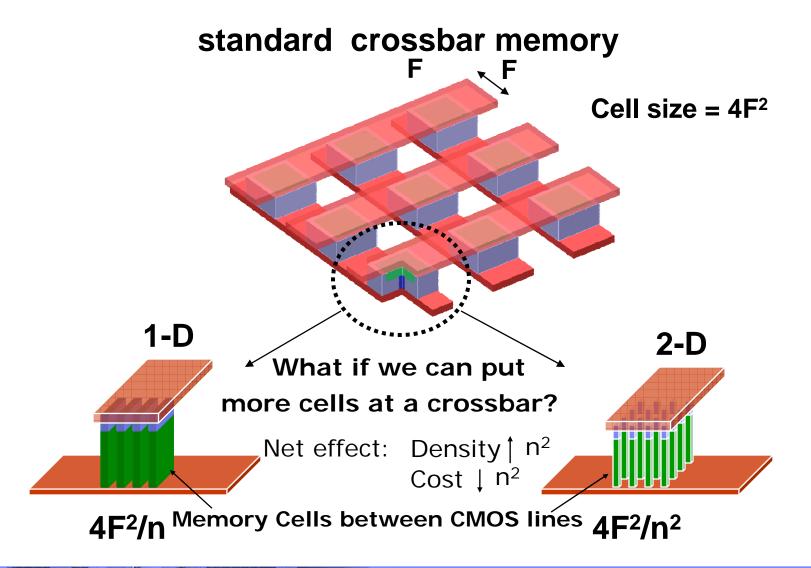

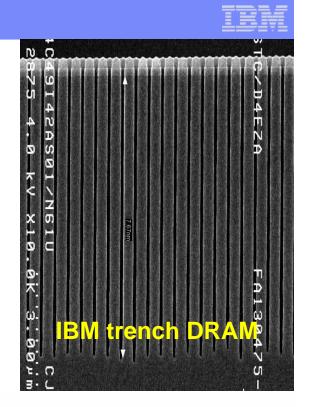

## Processing Cost and F<sup>2</sup>

- The bit cell size drives the cost of any memory

- Cell area is expressed in units of F<sup>2</sup> where F is the minimum lithographic feature of the densest process layer

- Half pitch dimension of metallization connecting drain and source for ICs

- MR sensor width in magnetic recording

#### Cell areas

- DRAM  $8F^2 \rightarrow 6F^2$

- NAND  $4F^2 \rightarrow 2F^2$

- SRAM 100F<sup>2</sup>

- MRAM 15F<sup>2</sup> -- 40F<sup>2</sup>

- − Hard Disk 0.5F<sup>2</sup> → 1F<sup>2</sup>

| CORPORATION . |      | A DESCRIPTION OF          | STRA 1  |                                |

|---------------|------|---------------------------|---------|--------------------------------|

| <b>IBN</b>    | ED.C | 000                       | roh     |                                |

|               |      | SEd                       |         | and a transformer              |

|               |      | And I Real Property lies, | A DECKS | an in the second second second |

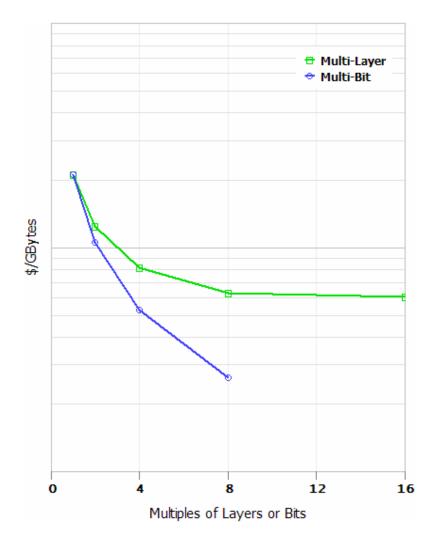

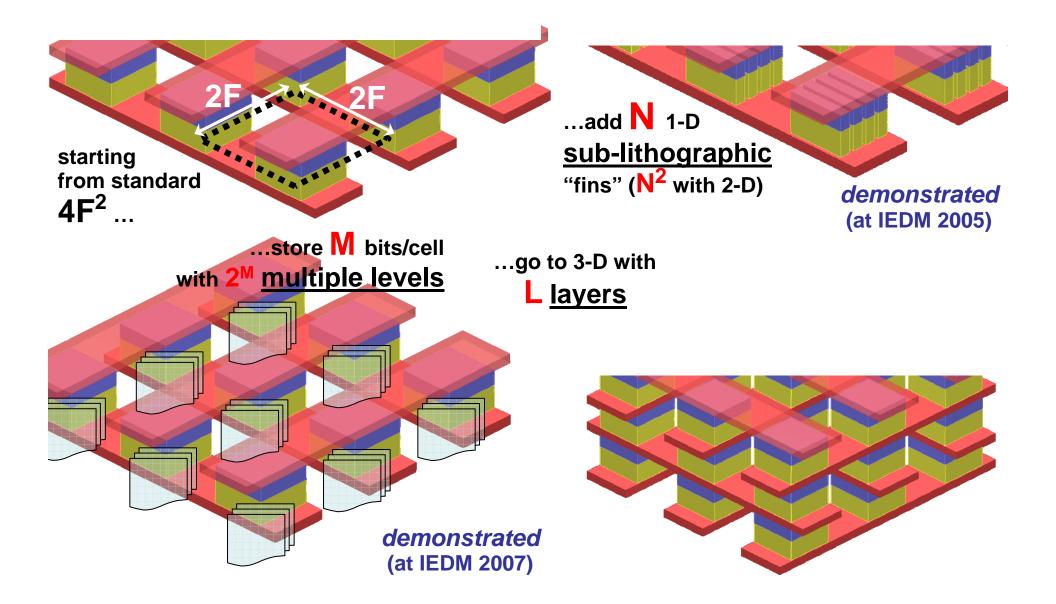

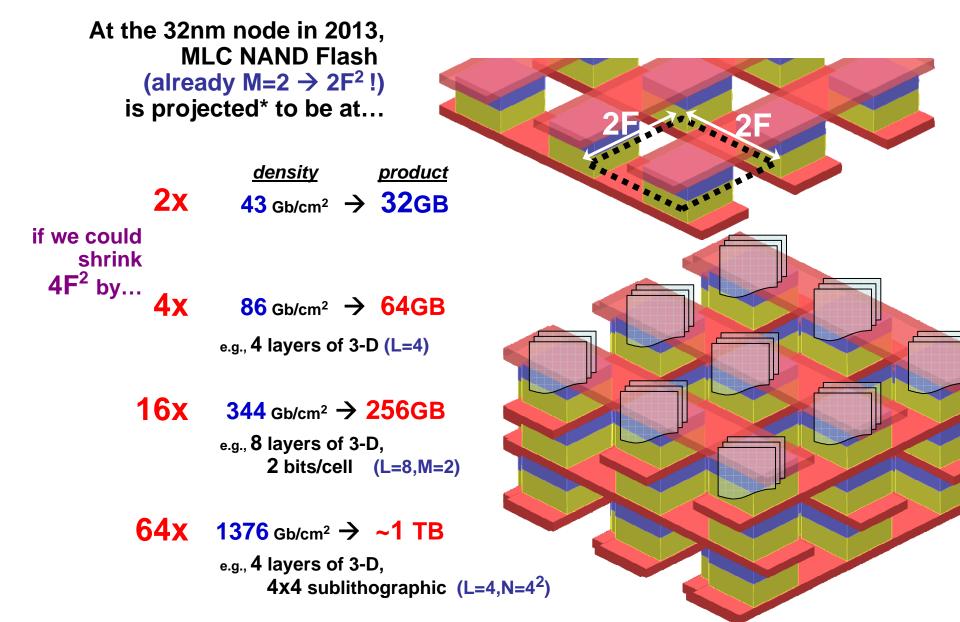

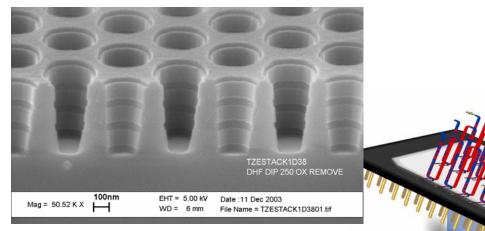

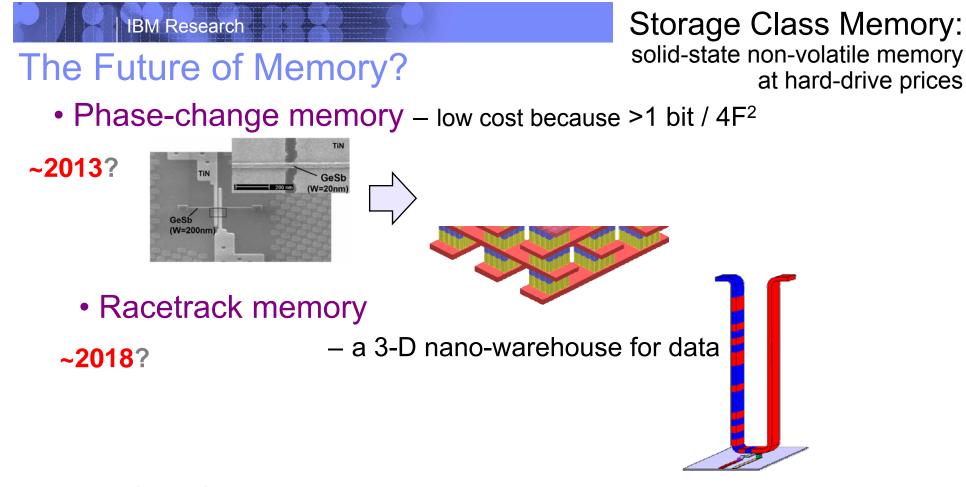

## What's next after CD reaching Physical Limit?

- Beyond the lithographic CD limit, there are 2 ways to continue Moore's Law of Cost Reduction in Semiconductor Memories:

- Multi-bit per cell (MLC),

- Multi-layer stacking (3D).

- Multi-bits per cell is the more effective way, the combination is most powerful:

- 8-layer stack is probably the cost-effective limit for fully integrated stacking,

- 2 bits per cell is probable with Phase Change Memories,

- >2 bits would require more innovation.

#### IBM Research

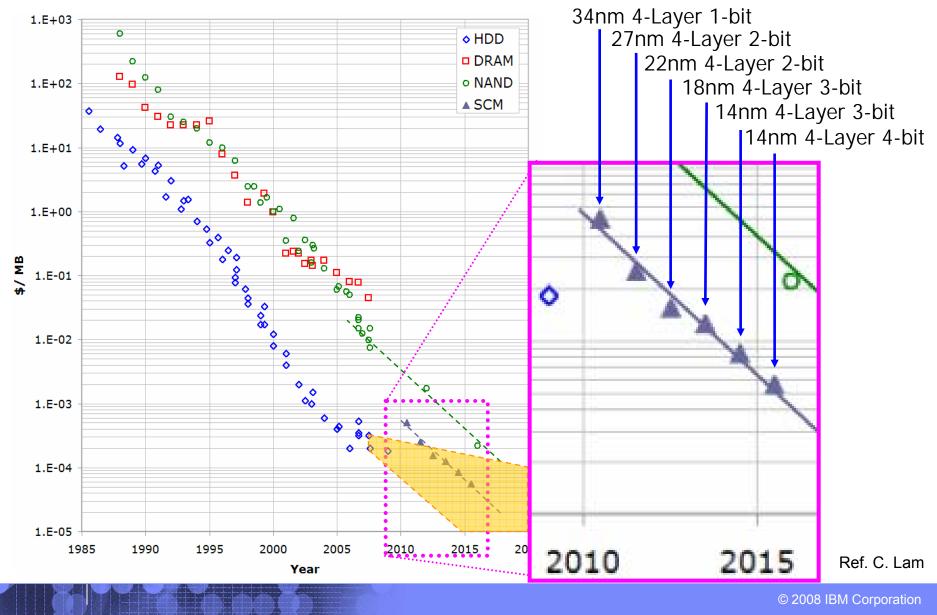

# **Storage Historic Price Trend and Forecast**

#### Universal Memory or Storage Class Memory Target Specifications

| *  | Access Time      | ~100-200 ns                        |

|----|------------------|------------------------------------|

| *  | Data Rate (MB/s) | 100                                |

|    | Endurance        | 10 <sup>9</sup> - 10 <sup>12</sup> |

|    | HER (/TB)        | <b>10</b> <sup>-4</sup>            |

| ** | MTBF (MH)        | 2                                  |

|    | On Power (mW)    | 100                                |

|    | Standby (mW)     | 1                                  |

|    | Cost (\$/GB)     | <5.5                               |

| Ţ  | CGR              | 35%                                |

Very challenging to achieve in combination

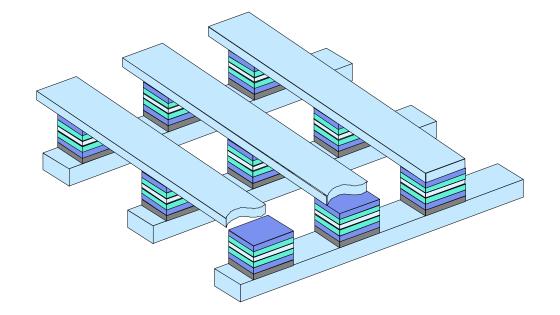

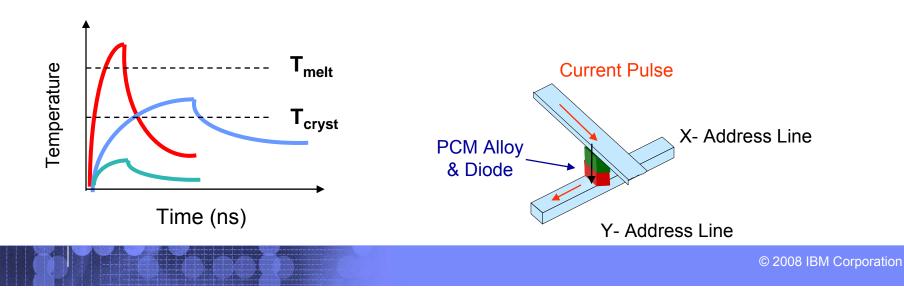

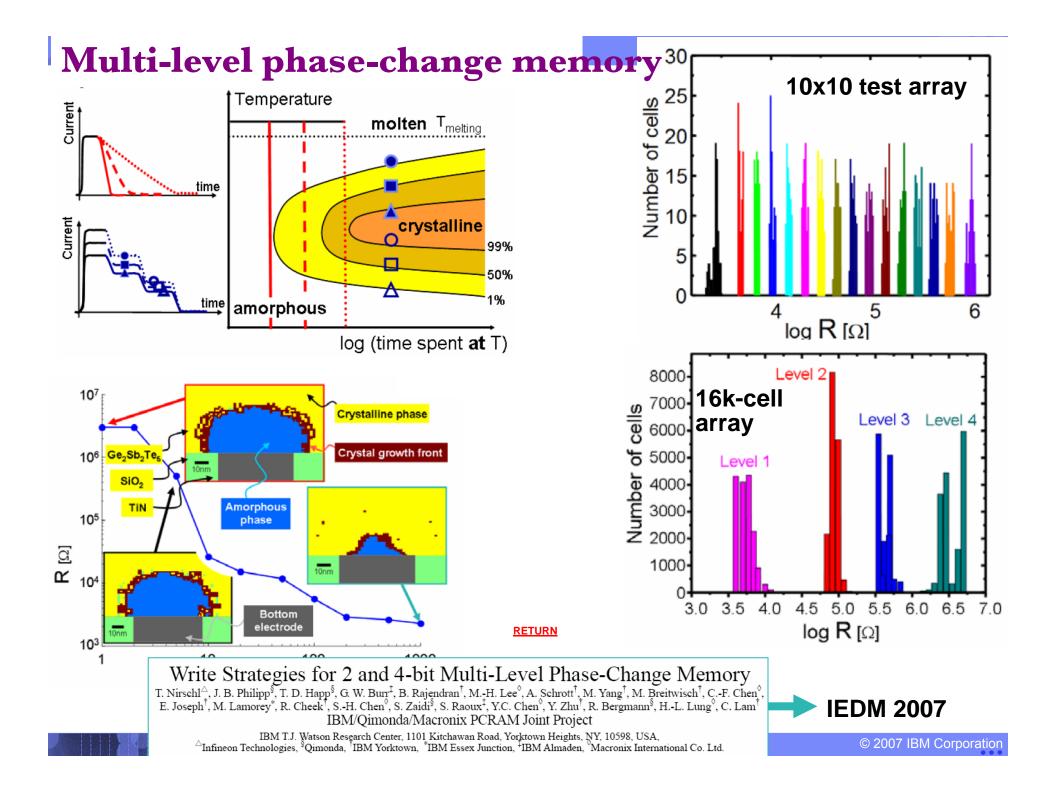

# SCM Basic Concepts: Phase Change Example

- Using a phase transition of a Ge-Sb-Te alloy to store a bit

- Ge-Sb-Te exists in a stable amorphous and a stable crystalline phase

- Phases have very different electrical resistances

- Transition between phases by controlled heating/cooling

- Write '1' : short (10ns) intense current pulse melts alloy crystal => amorphous

- Write '0' : longer (50ns) weaker current pulse re-crystalizes alloy => crystalline

- Read : short weak pulse senses resistance, but doesn't change phase

- Issue: rectifying diode materials for high-ON current density (> 10<sup>7</sup> A/cm<sup>2</sup> needed for PCM) and ultra-low OFF current density (< 1 A/cm<sup>2</sup>).

## A Brief History of Phase Change Memory

#### 1962 A.D. Pearson et al reported switching pheonomena in AsTeI (Advanc. Galss Tech. p357)

|            | 8 Ovshinsky published Phase Change Threshold Switching                                                                                                                                       |               |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 196<br>197 | 9<br>0 R.G. Neale et al demonstrated a 256-bit Phase Change Memory                                                                                                                           |               |

| 197        | •                                                                                                                                                                                            |               |

| 197        | -<br>2 J. Feinleib et al demonstrated Reversible Optical Memory                                                                                                                              |               |

| 197        |                                                                                                                                                                                              |               |

| 197        | 4                                                                                                                                                                                            |               |

| 197        | 5                                                                                                                                                                                            |               |

| 197        | 6                                                                                                                                                                                            | We            |

| 197        | 7                                                                                                                                                                                            | sitio         |

| 197        | 8                                                                                                                                                                                            | state         |

| 197        | 9                                                                                                                                                                                            | obse          |

| 198        | 0                                                                                                                                                                                            | als,          |

| 198        |                                                                                                                                                                                              | cove          |

| 198        |                                                                                                                                                                                              | inclu         |

| 198        |                                                                                                                                                                                              | teria<br>or a |

| 198        |                                                                                                                                                                                              | thos          |

| 198        | -                                                                                                                                                                                            | Su            |

| 198        |                                                                                                                                                                                              | intri         |

| 198        |                                                                                                                                                                                              | gy g          |

| 198        |                                                                                                                                                                                              | an a          |

| 190        | 9<br>0 Panasonic introduced R/W Phase Change Optical Disk Drive                                                                                                                              | $\Delta E$    |

| 199        |                                                                                                                                                                                              | sitio         |

| 199        | -                                                                                                                                                                                            |               |

| 199        | -                                                                                                                                                                                            |               |

| 199        | -                                                                                                                                                                                            |               |

| 199        |                                                                                                                                                                                              |               |

| 199        | -                                                                                                                                                                                            |               |

| 199        |                                                                                                                                                                                              |               |

| 199        | 8                                                                                                                                                                                            |               |

| 199        | 9 Ovonyx formed                                                                                                                                                                              |               |

|            | BAE licensed Ovonic Unified Memory (OUM) from Ovonyx 11/4/1999                                                                                                                               |               |

| 200        | 0 Intel Capital invested in Ovonyx and licensed OUM from Ovonyx 2/8/2000                                                                                                                     |               |

|            | STMicro licensed OUM from Ovonyx and announce Joint Development Project 12/21/2000                                                                                                           |               |

| 200        | -                                                                                                                                                                                            |               |

| 200        |                                                                                                                                                                                              |               |

| 200        | 3 STMicro and Ovonyx expanded scope of OUM license and extended 1DP 2/4/2003                                                                                                                 |               |

|            | Samsung published first paper on PRAM in VLSI'03                                                                                                                                             |               |

|            | Hitachi published first paper on PRAM in IEDM'03                                                                                                                                             |               |

| 200        | 4 Samsung annouced full-scale PRAM production in 2006 8/23/2004                                                                                                                              |               |

|            | Nanochip licensed OUM from Ovonyx for Micro-Electro_Mechanical Systems (MEMS) based storage 8/31/2004                                                                                        |               |

| 200        | 5 Elpida licensed OUM from Ovonyx 2/3/2005                                                                                                                                                   |               |

|            | Philips Research published first paper on PKAM in Nature Materials April Issue                                                                                                               |               |

|            | IBM, Infineon and Macronix announced Joint Research Initiative on Phase Change Memory 5/23/2005                                                                                              |               |

| 200        | Samsung announced S12Mb PRAM availability in 2008 to replace NOR Flash 12/28/2005<br>5 ITPL of Triuwan and Jacob some worders. Dewoor bin Namus, DevMOS and Winbord Formed DCM Alliance 0/26 | nooe          |

|            | 6 ITRI of Taiwan and local memory vendors - PowerChip, Nanya, ProMOS and Winbond formed PCM Alliance 9/26/                                                                                   | 2006          |

| 200        | 7 Ovonyx and Qimonda Sign Technology Licensing Agreement for Phase Change Memory 1/16/2007                                                                                                   |               |

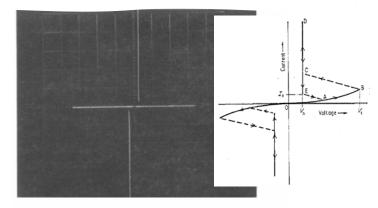

#### REVERSIBLE ELECTRICAL SWITCHING PHENOMENA IN DISORDERED STRUCTURES

Stanford R. Ovshinsky Energy Conversion Devices, Inc., Troy, Michigan (Received 23 August 1968)

A rapid and reversible transition between a highly resistive and conductive state effected by an electric field, which we have observed in various types of disordered semiconducting material, is described in detail. The switching parameters and chemical composition of a typical material are presented, and microscopic mechanisms for the conduction phenomena are suggested.

We describe here a rapid and reversible transition between a highly resistive and a conductive state effected by an electric field which we have observed in various types of disordered materials, particularly amorphous semiconductors<sup>1,2</sup> covering a wide range of compositions. These include oxide- and boron-based glasses and materials which contain the elements tellurium and/ or arsenic combined with other elements such as those of groups III, IV, and VI.

Such amorphous materials can be described as intrinsic semiconductors<sup>3,4</sup> with an optical energy gap  $E_g$  typically between 0.6 and 1.4 eV and an activation energy<sup>3</sup> for electrical conduction  $\Delta E$  between 0.7 and 1.6 eV depending on composition.

indicate that the

ing (in atomic percent) 48 at.% tellurium, 30 at.% arsenic, 12 at.% silicon, and 10 at.% germanium. The specimen was an evaporated film,  $5 \times 10^{-5}$  cm thick, between two carbon electrodes with a contact area of about  $10^{-4}$  cm<sup>2</sup>. This material has a resistivity at 300°K of  $\rho = 2 \times 10^{7} \Omega$  cm,  $\Delta E$  = 1.0 eV, and a positive thermopower.

Figure 1 shows oscilloscope pictures of (a) the I-V characteristic, (b) the voltage V across the unit, and (c) the current I passing through the above unit as a function of time. In this case, a 60-Hz ac voltage was applied across the unit and a  $10^4 - \Omega$  load resistor was used. The I-V curve is independent of frequency to at least  $10^6$  Hz.

The major features of the switching phenomena shown are the following: (1) The I-V character-

FIG. 1. Response of switching unit to 60-Hz voltage. (a) *I-V* characteristic: vertical, 2 mA/div; horizontal, 5 V/div. (b) Voltage: vertical, 5 V/div; horizontal, 5 msec/div. (c) Current: vertical, 20 mA/div; horizontal, 5 msec/div.

| CONTRACT. | 1916 | A DESIGNATION OF | approx (C) (C) |                               |   |

|-----------|------|------------------|----------------|-------------------------------|---|

| IBN       | 1 Do | 00               | oro            |                               |   |

|           |      | SE               |                | if in the second              | - |

|           |      |                  |                | state of some law and the law |   |

#### A Long "Pause" 1962 A.D. Pearson et al reported switching pheonomena in AsTeI (Advanc. Galss Tech. p357) 1968 Ovshinsky published Phase Change Threshold Switching 1969 1970 R.C. Neale et al demonstrated a 256-bit Phase Change Memory 1971 1972 J. Feinleib et al demonstrated Reversible Optical Memory 19/31974 1975 1976 1977 1978 1979 1980 256 bits 25V 7.5mA 15ms, 25V 150mA 6us 1981 1982 1983 1984 Intel, ECD 1970 1985 1986 1987 1988 1989 1990 Panasonic introduced R/W Phase Change Optical Disk Drive 1991 1992 1993 The energy required to melt the Phase Change Memory 1994 1995 Flement scales with CD ... 1996 1997 1998 1999 Ovonyx formed BAE licensed Ovonic Unified Memory (OUM) from Ovonyx 11/4/1999 2000 Intel Capital invested in Ovonyx and licensed OUM from Ovonyx 2/8/2000 STMicro licensed OUM from Ovonyx and announce Joint Development Project 12/21/2000 2001 2002 2003 STMicro and Ovonyx expanded scope of OUM license and extended 10P 2/4/2003 Samsung published first paper on PRAM in VLSI'03 Hitachi published first paper on PRAM in IEDM'03 2004 Samsung annouced full-scale PRAM production in 2006 8/23/2004 Nanochip licensed OUM from Ovonyx for Micro-Electro\_Mechanical Systems (MEMS) based storage 8/31/2004 2005 Elpida licensed OUM from Ovonyx 2/3/2005 Philips Research published first paper on PRAM in Nature Materials April Issue IBM, Infineon and Macronix announced Joint Research Initiative on Phase Change Memory 5/23/2005 Samsung announced 512Mb PRAM availability in 2008 to replace NOR Flash 12/28/2005 2006 ITRI of Taiwan and local memory vendors - PowerChip, Nanya, ProMOS and Winbond formed PCM Alliance 9/26/2006 2007 Ovonyx and Qimonda Sign Technology Licensing Agreement for Phase Change Memory 1/16/2007

#### IBM Research

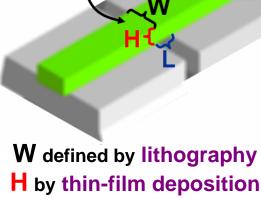

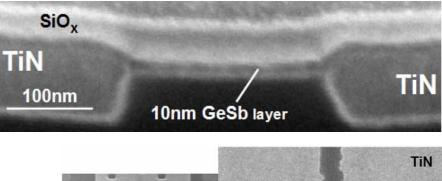

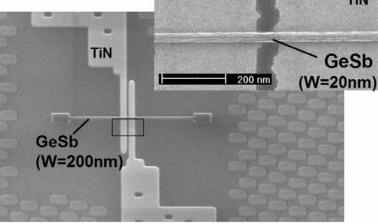

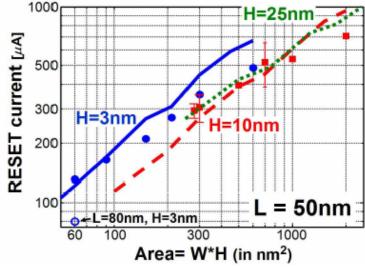

# Phase-Change Nano-Bridge

Prototype memory device with ultra-thin (3nm) films demonstrated Dec '06

•  $3nm * 20nm \rightarrow 60nm^2$

Phase-change "bridge"

Che New Hork Eimes

$\rightarrow$  phase-change scales Fast (<100ns SET)</p> Low current (< 100μA RESET)</p> current [µA] Applied voltage IV 0.5 (e) SET 60 80 120 20 40 100 Time [ns] current [µA] .6 Applied Voltage [V] 20 0 8 20 40 60 80 100 120 Time [ns]

≈ Flash roadmap for **2013**

Current scales with area

# **Crossbar Memory Fundamentals**

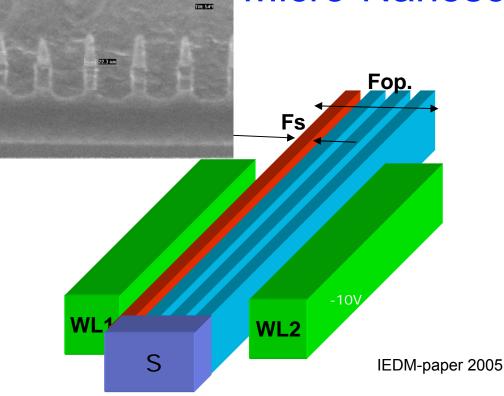

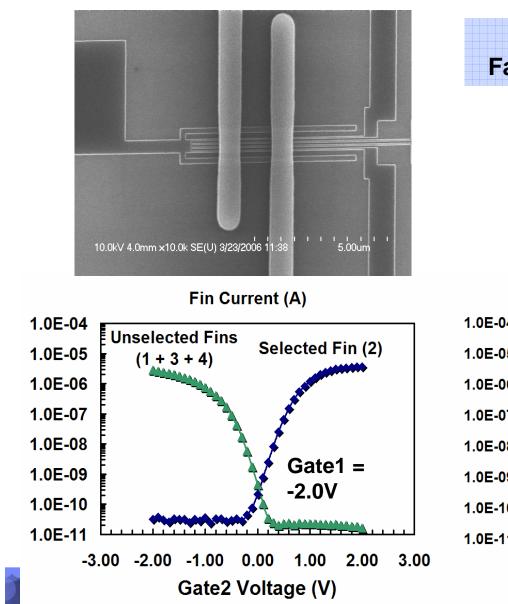

# Micro-Nanoscale Decoder

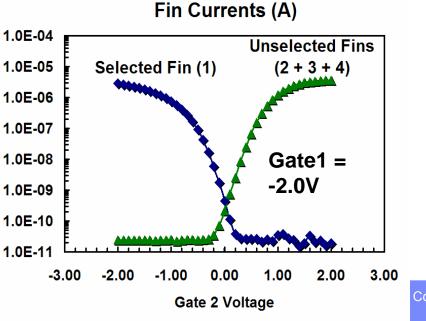

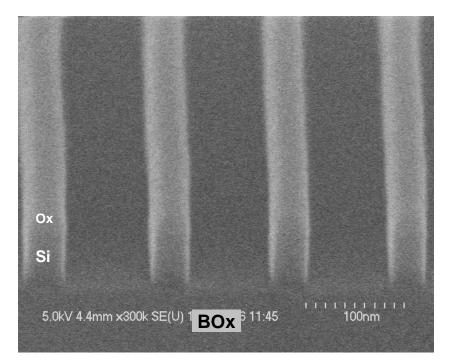

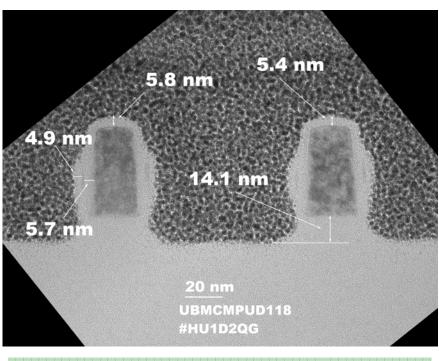

**Current in Fins**

Absolute

- Sub lithographic feature is selected by moving depletion across the fine structure

- Modulating signal is brought in by lithographically defined lines

IBM

Research

• Fins down to sub 20 nm have been addressed

#### IBM Almaden Research Center

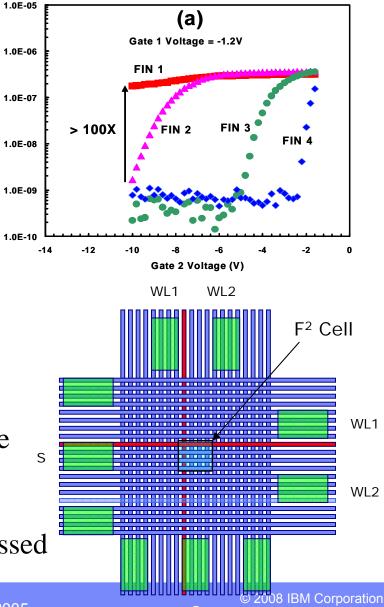

## **MNAB Concept Demonstrated**

100nm Pitch MNAB Devices Fabricated by E-Beam Lithography

> Obtained Fully Functional Devices

Selectivity > 10<sup>5</sup>

Corporation

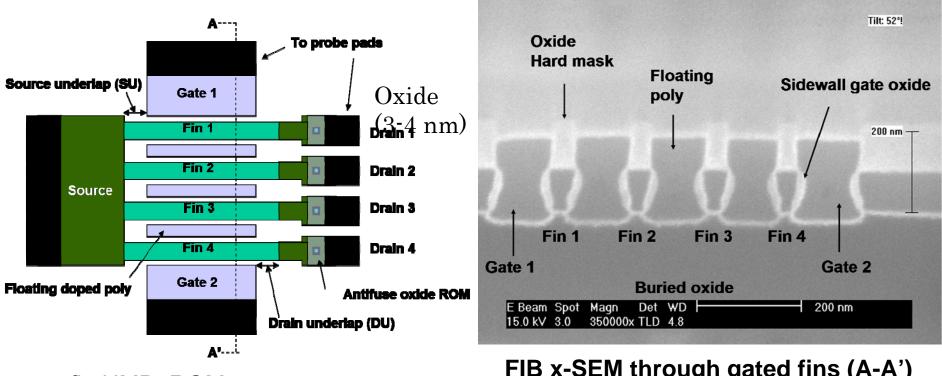

# Combining Micro-Nano Decoder and ROM

4-fin UMB+ROM test structure

FIB x-SEM through gated fins (A-A')

✓ Successful integration of UMB with memory element (2 terminal oxide antifuse ROM)

✓ Verified operation over all bit sequences for 4-fin UMB+ROM

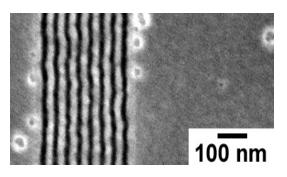

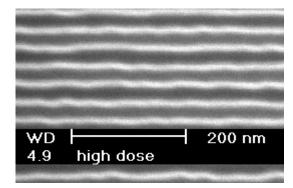

# **Nanoscale Patterning Techniques**

# **Self Assembly**

**IBM Research**

#### **Spacers**

Frequency doubling – 40 nm to 20 nm pitch (IBM) Nanoimprint Lithography

**Princeton / Nanonex**

- Litho Tool: 193nm immersion at 1.35 NA, next?

- Various nanoscale patterning techniques exist.

- Simple regular line / space patterns possible.

#### Silicon Fins Resulting from Oxide and Imprint Etch Masks

- Critical Dimension Control

- Side-Wall Profile

- ✓ Line-Edge Roughness

#### Silicon Fins Ready for Ion-Implant Lithography and Processing

Mark Hart, et al.

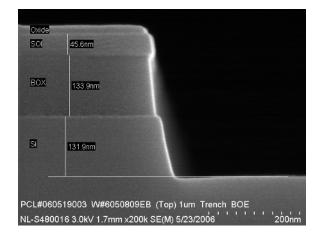

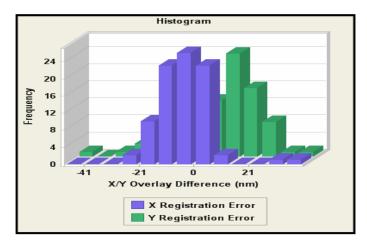

## Mix-and-Match Overlay of SFIL to Optical Lithography

### -- To Align Optical Levels with Imprint Level --

Generate "Zero-Level" Marks in Wafer via 193nm Lithography and Etch to Ensure they Survive the Full MNAB Process Build

Align both Imprint Level and Subsequent Optical Levels to These Zero-Level Marks

## -- Using This Approach --

Demonstrated Sub-20nm (Mean+3σ) Overlay Between 193nm Litho Zero-Level and Imprint Over Full 200mm Wafers

Routinely Achieving Sub-50nm Overlay in Approximately 75% of Fields

# Paths to ultra-high density me

# Paths to ultra-high density memory

\* 2006 ITRS Roadmap

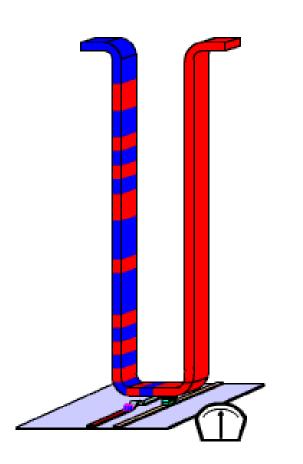

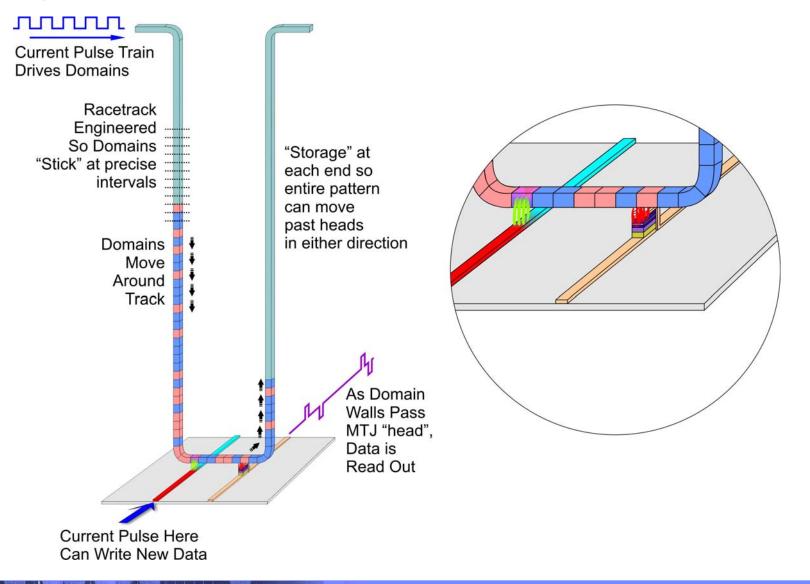

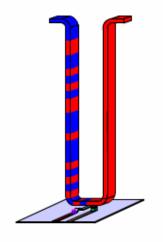

#### Magnetic Racetrack Memory: a 3-D shift reg. Memory

•Data stored as pattern of domains in long nanowire or "racetrack" of magnetic material.

•Data stored magnetically and is non-volatile.

•Current pulses move domains along racetrack - *no moving parts, just the patterns move.*

•Each memory location stores *an entire bit pattern* (10, 100, 1000 bits?) rather than just a single bit.

#### Magnetic Racetrack Memory Concept

#### IBM Research

#### Magnetic Race-Track Memory

- Information stored as domain walls in vertical "race track"

- Data stored in the third dimension in tall columns of magnetic material

- Domains moved around track using nanosecond pulses of current

- 10 to 100 times the storage capacity of conventional solid state memory

Magnetic Race Track Memory S. Parkin (IBM), *US patents* 6,834,005 (2004) & 6,898,132 (2005)

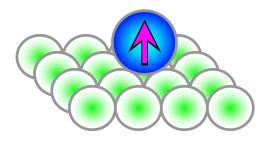

# Magnetic anisotropy at a surface

- Free atomic spin is rotationally invariant: all spin orientations are degenerate.

- Loss of rotational symmetry breaks degeneracy of spin orientations.

Magnetic field dependence varies with angle of magnetic field.

#### IBM Research

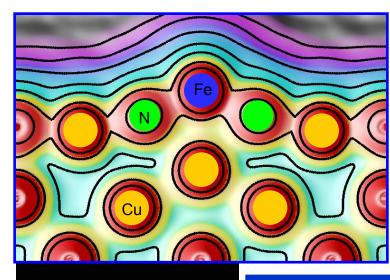

#### Future?: Large Magnetic Anisotropy for Single Atom Memory

- The energy that is required to change the direction of a single spin on CuN measured.

- Large single-atom magnetic anisotropy for iron of about 6 meV.

- About 50x weaker anisotropy for manganese on same surface.

- Spin excitation spectroscopy reveals spin energy levels, including their magnetic field dependence.

- DFT calculations elucidate surface structure and leads to same total spin as experiment.

- GOAL: engineer very large magnetic anisotropy to demonstrate data storage.

• Atomic memory – "there's a lot of room at the bottom..."

~2030?

Science & Technology

# Thank you!