Transforming Nanodevices to Nanosystems

TITLE: Transforming Nanodevices to Nanosystems

SPEAKER: Max M. Shulaker, Stanford University

Tuesday, June 21st, 2016 11:30 AM – 1:00 pm

Texas Instruments (TI) Auditorium E-1

2900 Semiconductor Drive

Santa Clara, CA

map

Admission FREE ($5 donation requested). Please register here.

ABSTRACT:

The computing demands of future data-intensive applications far exceed the capabilities of today’s electronics, and cannot be met by isolated improvements in transistor technologies or integrated circuit (IC) architectures alone. Transformative nanosystems, which leverage the unique properties of emerging nanotechnologies to create new IC architectures, are required to deliver unprecedented performance and energy efficiency. However, emerging nanomaterials and nanodevices suffer from significant imperfections and variations. Thus, realizing working circuits, let alone transformative nanosystems, has been infeasible.

As a case-study for realizing nanosystems, I will present my work on carbon nanotube field-effect transistors (CNFETs), a leading candidate for energy-efficient and high-performance digital systems. Unfortunately, substantial imperfections and variations inherent to carbon nanotubes (CNTs), combined with low current densities, restricted demonstrations to stand-alone transistors or logic gates, with severely limited performance, yield, and scalability. I will describe techniques to overcome these major challenges through a combination of new CNT process techniques and CNFET circuit design solutions. This imperfection-immune paradigm transforms CNTs from solely a scientifically-interesting material into working nanosystems such as the first microprocessor [Nature 2013] and the first digital sub-systems [ISSCC 2013, JSSC 2014, ACS Nano 2014] built entirely using CNFETs. These are the first system-level demonstrations among promising emerging nanotechnologies for high-performance and highly energy-efficient digital systems. This approach also enables high-performance CNFETs with the highest current-drive to-date (which are, for the first time, competitive with comparably-sized silicon-based transistors from commercial foundries [IEDM 2014]). All of the fabrication and design techniques are VLSI-compatible, and can be applied to arbitrary technology nodes; to illustrate, I will describe recent results from a 14 nm-node CNFET [IEDM 2015].

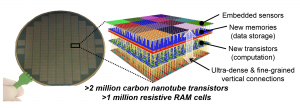

Beyond specific CNT technologies, I will also present my work on building new architectures to achieve high degrees of energy efficiency for emerging data-intensive applications. Such new architectures are naturally enabled by a range of beyond-silicon emerging nanotechnologies (including CNTs). I will demonstrate the first monolithically-integrated three-dimensional (3D) nanosystem architectures [VLSI Tech. 2014, IEDM 2014] with vertically-integrated layers of logic, memory, and sensing circuits. These include the largest nanosystem yet fabricated using beyond-silicon emerging nanotechnologies, with over 2 million CNFETs and over 1 million Resistive Random Access Memory (RRAM) cells, all integrated vertically over a conventional silicon substrate with over 1 million silicon transistors (all fabricated at the Stanford Nanofabrication Facility). With dense and fine-grained connectivity between sensing, storage and computation, such nanosystems can capture terabytes of data from the outside world every second, and produce “processed information” by performing in-situ classification of the sensor data using on-chip accelerators designed using CNFET logic.

I will conclude by giving my vision for how the ubiquitous computing technology that is critical for meeting society’s challenges in the 21st century can be realized by harnessing the capabilities of multiple nanomaterials and nanodevices in complex nanosystems.

SPEAKER BIOGRAPHY:

Max Shulaker will be joining MIT in Electrical Engineering and Computer Science as a faculty member, having finished his PhD in Electrical Engineering at Stanford University under the supervision of Professor Subhasish Mitra and co-advised by Professor Philip Wong. He received his B.S. from Stanford University in Electrical Engineering. Max’s current research interests are in the broad area of nanosystems. His research results include the demonstration of the first carbon nanotube computer (highlighted on the cover of Nature, Sept. 2013), the first digital sub-systems built entirely using carbon nanotube FETs (awarded the ISSCC Jack Raper Award for Outstanding Technology-Directions Paper, 2013), the first monolithically-integrated 3D integrated circuits combining arbitrary vertical stacking of logic and memory (IEDM 2014), the highest-performance CNFETs to-date (IEDM 2014), and the first highly-scaled CNFETs fabricated in a VLSI-compatible manner (IEDM 2015). He was a Fannie and John Hertz Fellow and a Stanford Graduate Fellow.

AGENDA:

- 11:30 am – Registration & light lunch (pizza & drinks)

- Noon – Presentation & Questions/Answers

- 1:00 pm – Adjourn

Please register here.

Also, visit our Meetup Group.