# High Speed Interconnect Design and Characterization

Jay Diepenbrock April, 2014

#### Outline

- Signal Integrity what, why, and how?

- Electrical characteristics of interconnect structures

- basic properties determined by materials, dimensions, etc.

- measurement techniques and tools

- "Real world" component examples

- capacitors (e. g., decoupling)

- vias

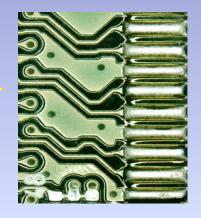

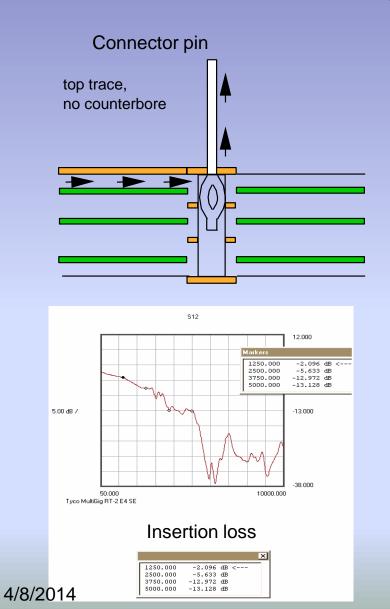

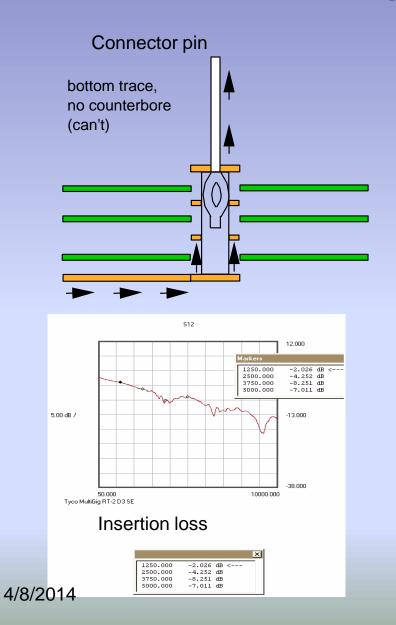

- connectors

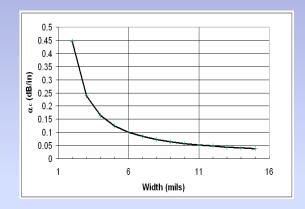

- Attenuation

- what is it?

- what causes it

- what are its effects?

- Resources and References

4/8/2014 2

#### What is Signal Integrity?

- Maximizing probability of delivering a signal from point A to point B without errors

- Managing signal quality, shape, etc. as seen by receiver circuits

- It's all about rise time, discontinuities, and frequency dependent losses

- Signal speeds, frequencies increasing

- Spatial resolution and frequency spectrum directly related to rise time

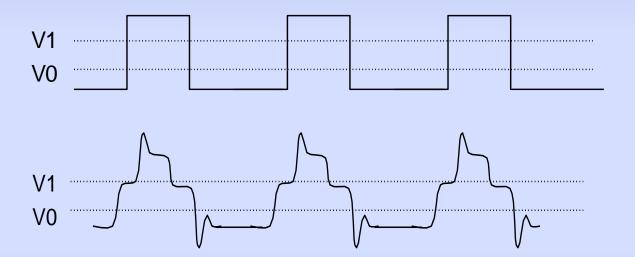

#### Ideal signal

- square edges,

- no noise,

- no interaction

Real signal

- nasty edges,

- noise,

- reflections

#### Signal Distortion

#### What goes in

#### What comes out

- Why?

- What can be done about it?

#### What is Signal Integrity?

- Multidisciplinary

- Analog

- Digital Signal Processing

- Complex signal modulation

- Equalization

- Error detection and correction

- Packaging

- "Black Magic" fields of

- Electromagnetics

- Radio Frequency (RF)

- Microwaves

- Transmission Lines

- Power supplies and distribution

- Software layout, analysis

- Testing

"Digital is just a special case of **analog**" – G. Philbrick, ca. 1950

#### Electrical characteristics of interconnects

- DC

- resistance

- opens/shorts

- HiPot

- Insulation resistance

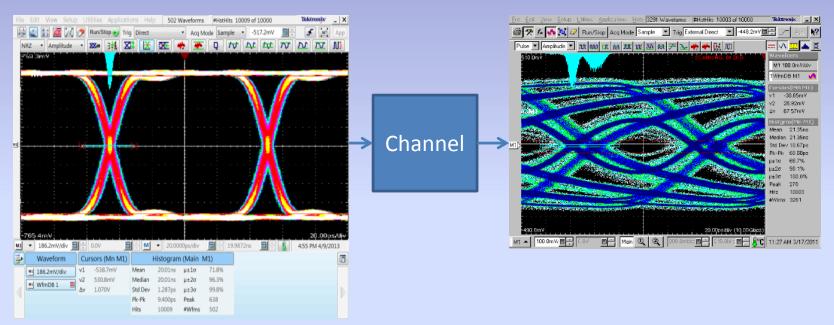

- AC, low frequency quantities and measurements

- capacitance

- inductance

- impedance

- AC, high frequency quantities and measurements

- impedance

- attenuation

- crosstalk

- jitter and eye patterns

4/8/2014 6

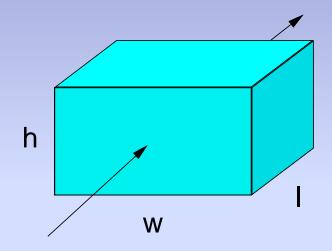

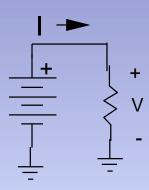

#### DC resistance

causes DC voltage drop, V=I\*R

- bulk resistivity =

- $\rho \Omega$ -cm or  $\rho_s \Omega$ /square

$$R = \rho^* \text{ I/(h*w)} = \rho_s^* \text{ I/w}$$

"sheet" resistivity # squares

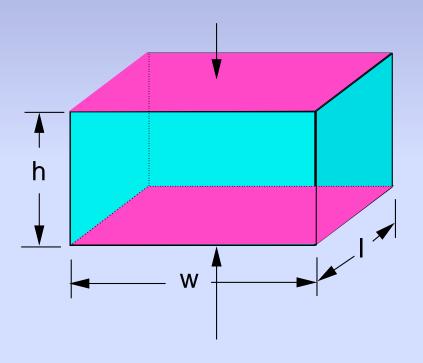

### Capacitance

stores charge, Q=V\*C, V= 1/C∫i dt

- $C=\varepsilon^*I^*w/h = \varepsilon^*A/h$ , where

- A = surface area of plates

- h = plate separation

- $\varepsilon = \varepsilon_r * \varepsilon_0$ , with  $\varepsilon_r = \text{material relative permittivity and}$   $\varepsilon_0 = \text{permittivity of air} = 8.854 \times 10 12 \text{ F/m}$

- typical  $\varepsilon_r$  values:

- air = 1.0

- PTFE = 2.0 (lower if expanded)

- FR-4 = 4.5

- Example:

- 1x1" FR-4 PCB plate,

- 10 mil spacing between planes

- C = 101 pF

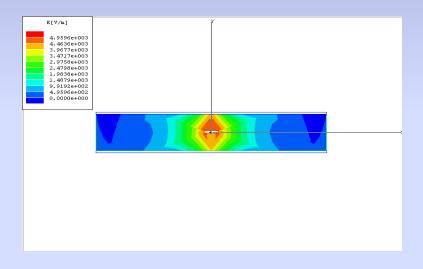

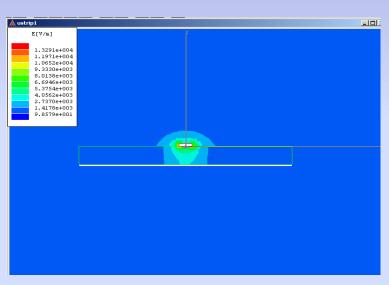

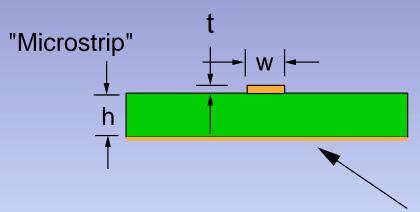

#### Capacitance

#### Complications:

- fringing fields with narrow lines

- inhomogeneous dielectrics (e. g., microstrip)

- Temperature, frequency dependence

(stripline field plot)

(microstrip field plot)

Measurement: LCR meter, impedance bridge, etc. (must specify freq.)

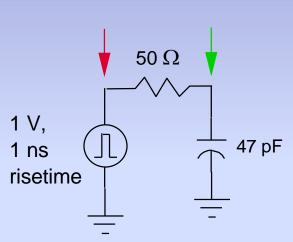

### Capacitance

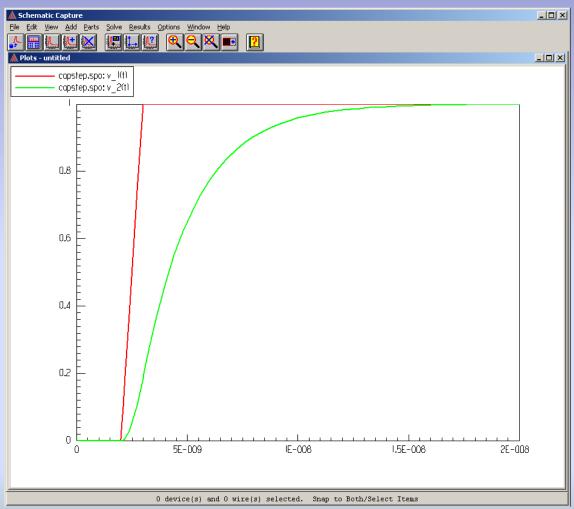

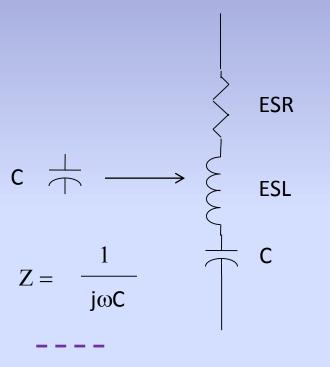

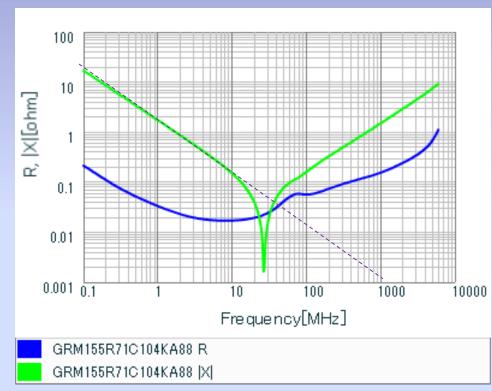

### Capacitance – real capacitors

(when is a capacitor not a capacitor?)

$Z = R + j\omega L + \frac{1}{j\omega C}$

Plot courtesy of muRata Erie

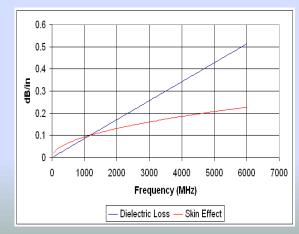

#### **Dielectric Loss**

**Recall,**  $\gamma = \sqrt{(R + jwL)(G + jwC)} = \alpha + j\beta$

and attenuation = 20

$$\log_{10}e^{Re \gamma}$$

= 20  $\log_{10}exp\sqrt{(RG-\omega^2LC)}$

- ♦ Dielectric constant of the medium,  $\varepsilon = \varepsilon (1 j \tan \delta_1)$ , so  $G = \sigma C/\varepsilon = \sigma C/D_k = \omega C \tan \delta = \omega C \tan D_f$  Increasing frequency -> shunt losses

- Typical values:

| Material                                | 3   | tan $\delta$ |

|-----------------------------------------|-----|--------------|

| FR-4 (normal glass-epoxy card material) | 4.5 | 0.02         |

| NELCO 4000-13                           | 3.7 | 0.008        |

| Megtron-6                               | 3.5 | 0.005        |

| PTFE (Teflon)                           | 2.1 | 0.0003       |

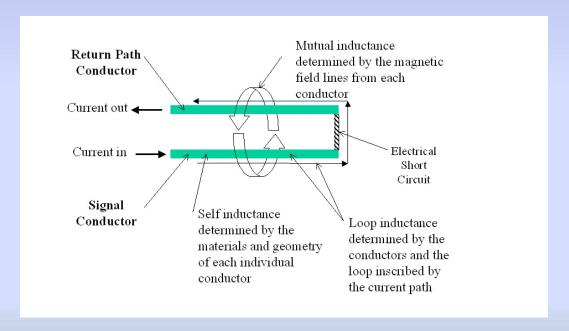

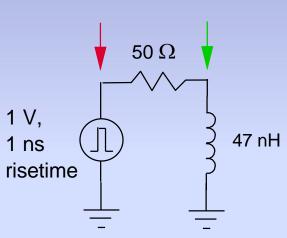

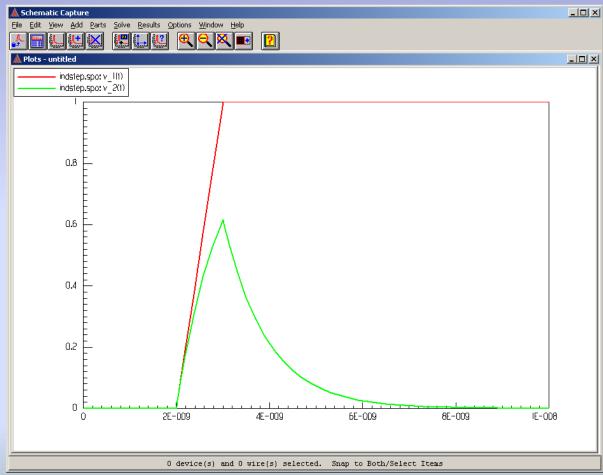

#### Inductance

opposes AC current flow, v = L di/dt

- Internal inductance,  $L = \mu/8\pi$  H/m

- where  $\mu = \mu_r \mu_0$ , with  $\mu_r =$  material relative permeability,  $\mu_0 =$  permeability of free space  $= 4\pi \text{ x} 10\text{-}7 \text{ H/m}$

- (round, infinitely long straight wire in

- free space w/ uniform current distribution)

#### Note:

- independent of wire diameter

- free space no adjacent conductors!

#### Inductance

- Complications:

- "Ground"

- loop inductance vs. self-inductance

- other adjacent conductors, return path

### Inductance - real wires

- L = 0.002 I \* [2.3 log10 ((4 I / d) 0.75)] uH, where I = wire length, cm d = wire diameter, cm

- Typical values:

| Wire size, AWG | Diameter, | Resistance, | Inductance, |

|----------------|-----------|-------------|-------------|

|                | cm        | mOhms/m     | nH/cm       |

| 20             | .0813     | 3.10        | 7.8         |

| 22             | .0642     | 4.94        | 8.2         |

| 24             | .0511     | 7.83        | 8.7         |

| 26             | .0404     | 12.5        | 9.2         |

| 28             | .0320     | 19.9        | 9.6         |

| 30             | .0254     | 31.7        | 10.1        |

## Inductance

# Impedance

- Causes AC voltage drop, v = i\*Z

- Units are Ohms, just like DC resistance

- In simplest form,  $Z = (L/C)^{1/2}$ , where L and C are per unit length

- You might ask: Why should I care?

- A better question: <u>When</u> should I care?

# Impedance

- Causes AC voltage drop, v = i\*Z

- Units are Ohms, just like DC resistance

- In simplest form, Z = (L/C)<sup>1/2</sup>, where L and C are per unit length

- You might ask: Why should I care?

- A better question: <u>When</u> should I care?

- Answer: when electrical length of interconnect segment > ~λ/10, or when electrical length of interconnect segment > ~trise/2 (electrical length = signal propagation delay in medium)

- Examples

- card microstrip (surface) wiring t<sub>prop</sub> ~= 170 ps/in.

- cable  $t_{prop} \sim = 110 \text{ ps/in.}$

Note: tprop.  $\sim$ = C/( $\epsilon_r$ )<sup>1/2</sup>, C = speed of light *in the medium* Note: Each segment has a different impedance (and prop. delay)!

So, what's the problem? The problem is discontinuities (interfaces)

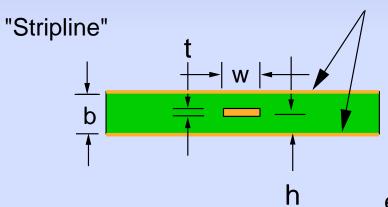

# Card wiring impedance

$$Z0 = \frac{87}{\sqrt{\epsilon_r} + 1.41} \ln \left( \frac{5.98*h}{0.8w + t} \right)$$

example: w=6, t=1.4, h=12 ->  $Z0=60 \Omega$

Ground planes

$$Z0 = \frac{60}{\sqrt{\epsilon_r}} \ln \left( \frac{4b}{0.67\pi w \left( 0.8 + \frac{t}{w} \right)} \right)$$

example: w=6, t=1.4, b=12, h=6 ->  $Z0=37 \Omega$

- Notes: 1. The stripline may not be vertically symmetric (can be unequal spacing to planes)

- 2. Other variations exist; e. g., covered microstrip (stripline w/o upper Ground plane) Reference: Blood: MECL Handbook

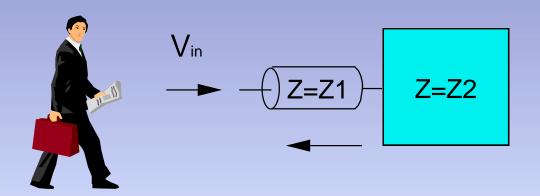

# Impedance

Reflection coefficient,

$$\rho = \frac{V_{refl}}{V_{in}} = \frac{Z2-Z1}{Z2+Z1}$$

(can be + or -, and may be called  $\Gamma$ )

Another useful relationship: VSWR =  $\frac{1+\rho}{1-\rho}$

# Impedance

Reflection coefficient,

$$\rho = \frac{V_{refl}}{V_{in}} = \frac{Z2-Z1}{Z2+Z1}$$

(can be + or -, and may be called  $\Gamma$ )

Imagine what would happen if you had this:

# Impedance measurement

#### Impedance Bridge

- AC source (oscillator) must specify frequency (ies)

- Measures R, L, C, Z looking into DUT

- Subject to inaccuracy due to

- resonance of DUT at measurement freq.

- discontinuities in DUT no position-dependent info

4/8/2014 22

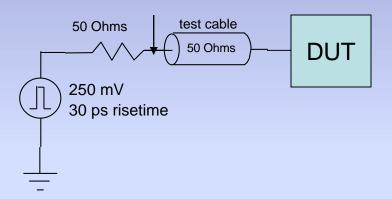

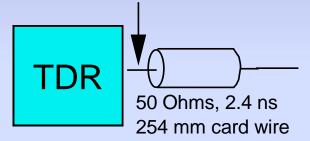

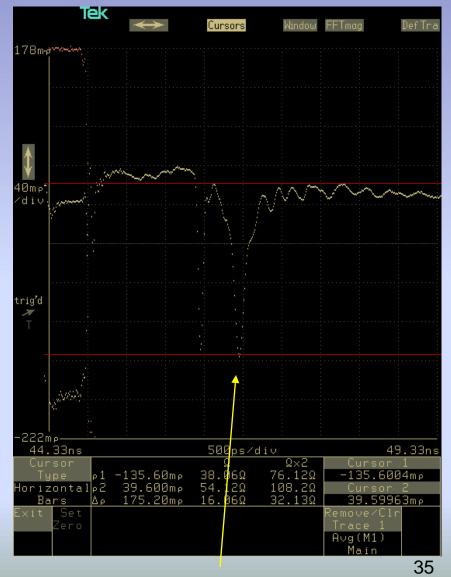

# Impedance measurement

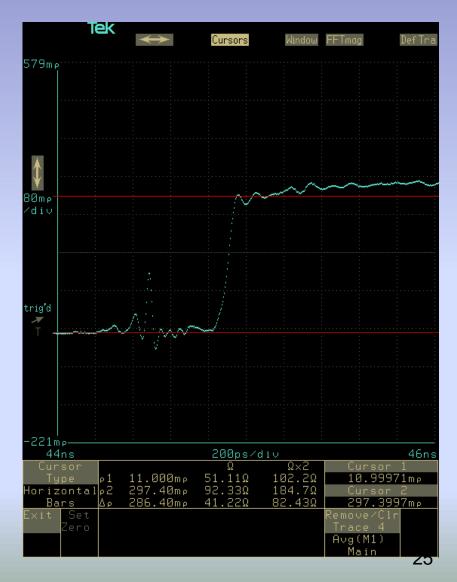

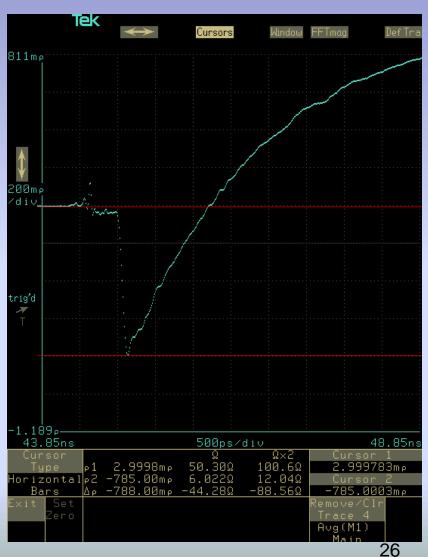

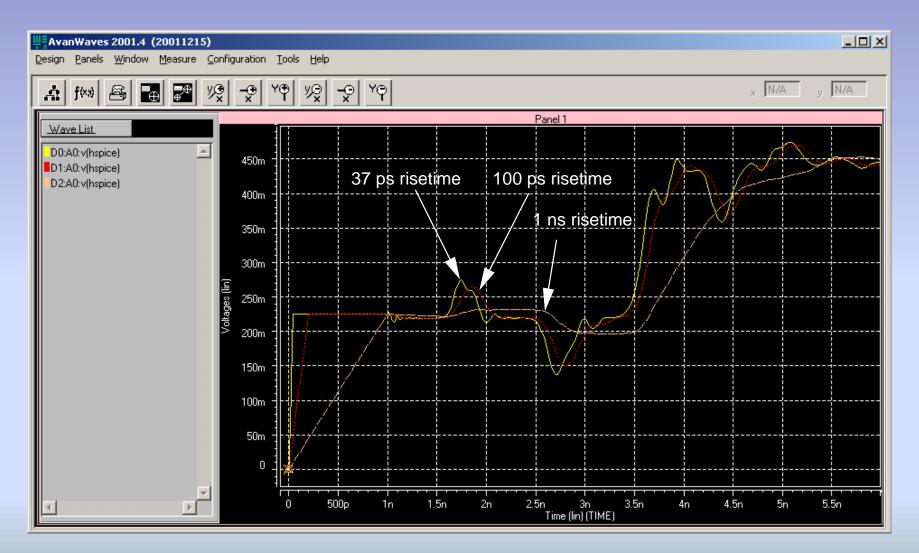

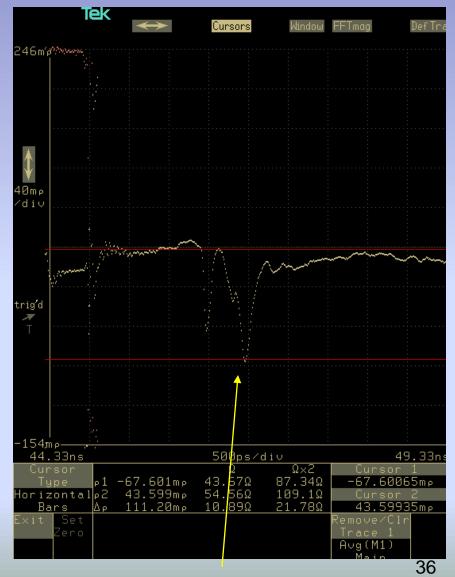

Time Domain Reflectometer (TDR)

Measure voltage here

- •time domain measurement measures Z vs. time (distance)

- •can be single-ended (shown) or differential (if equipment capable)

- accuracy, resolution degrade with

- loss in test cables and DUT

- probe effects (large ground loops, etc.)

- •risetime is everything!

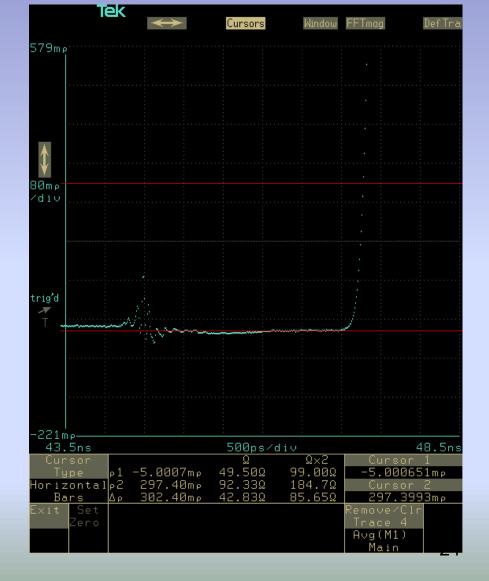

Matched line, open circuited end

measure voltage here

cursors:  $1=51.1 \Omega$

2=N/A

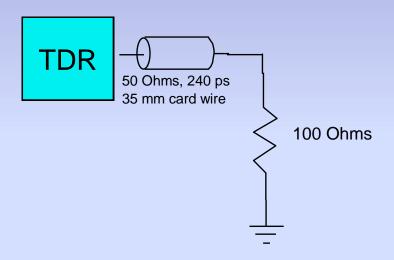

Matched line, mismatched resistive load

cursors: 1=51.1  $\Omega$

$2=92.33 \Omega$

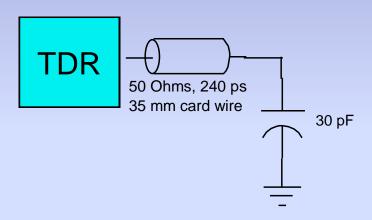

Matched line, capacitive load

cursors:  $1=50.30 \Omega$

$2=6.22 \Omega$

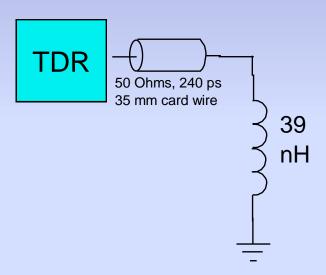

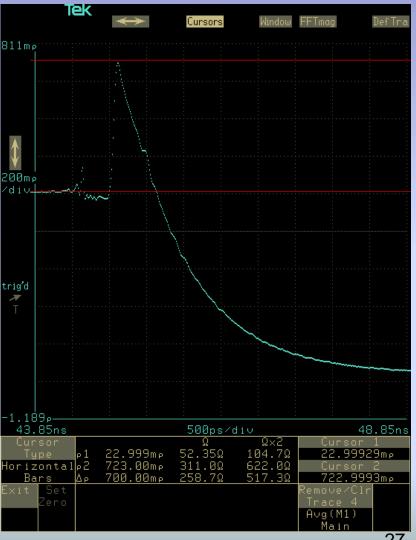

Matched line, inductive load

cursors: 1=52.35  $\Omega$

$2=311 \Omega$

4/8/2014

7 /

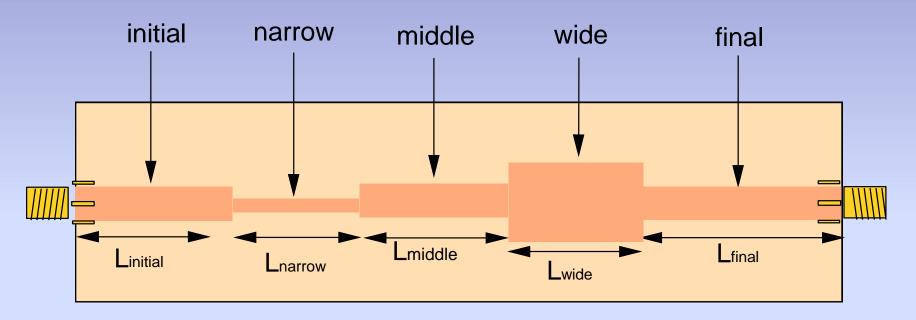

# Impedance example 5 "ugly" network

Winitial = 2.77 mm Wnarrow = 1.24 mm Wmiddle = Winitial Wwide = 7.58 mm

Wfinal = Winitial

Linitial = 53 mm Lnarrow = 20 mm Lmiddle = 56 mm Lwide = 20 mm Lfinal = 53 mm Zinitial =  $50 \Omega$ Znarrow =  $67 \Omega$ Zmiddle = Zinitial Zwide =  $31 \Omega$ Zfinal = Zinitial

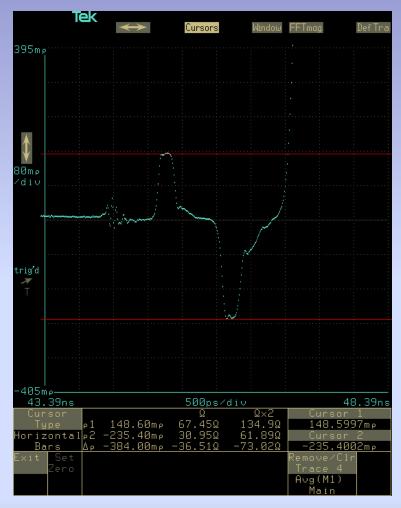

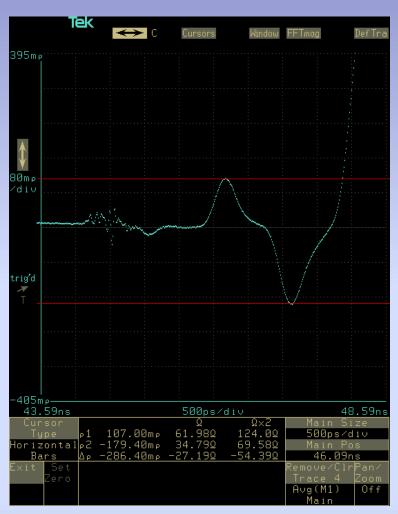

# "Ugly" network TDR plots

unfiltered: Zmin=30.95, Zmax=67.4

200 ps filter: Zmin=34.79, Zmax=61.98

# "Ugly" network simulation

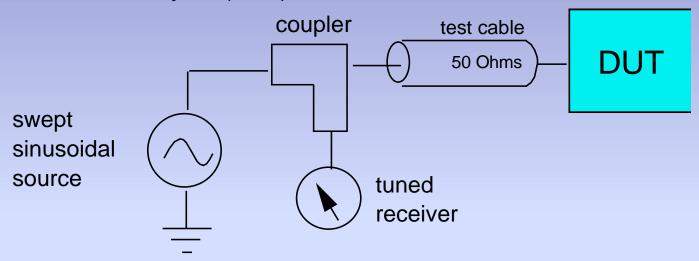

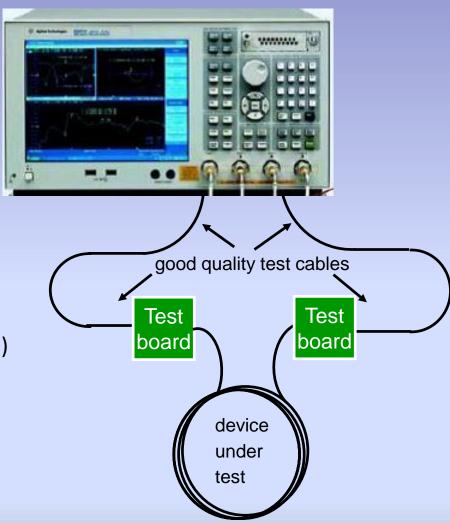

### Impedance measurement

Vector Network Analyzer (VNA)

- freq. domain measurement measures vs. frequency, typically. s parms.

- no spatial (distance) information

- can be single-ended (shown) or differential (if equipment capable)

- · accuracy, resolution degrade with

- •loss in test cables and DUT

- •fixture effects, including discontinuities

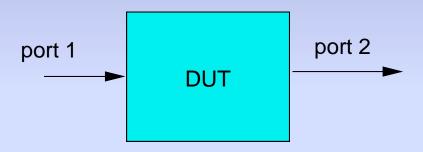

# s parameters

- Describe power transfer relationship between two ports of a DUT

- Normalized to 50 Ohms

- Can be related to other quantities; e. g., Z1 = Z0 (1+s11)/(1-s11)

sxy = power observed at port x due to power applied at port y

s11 = return loss (reflection) at port 1

s21 = insertion loss, port 1 to port 2

s22 = return loss (reflection) at port 2

4/8/2014 32

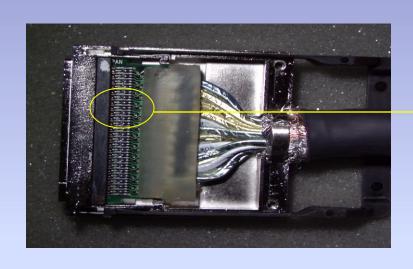

## Impedance Discontinuities

- Change in geometry of conductors

- width, thickness of signal conductor

- proximity to reference plane

- Change in surrounding materials (ε<sub>r</sub>)

- plastic insulators, connector body in connectors

- conductor dielectric, hot melt, overmold in cables

4/8/2014 33

# Impedance Discontinuities

### Vias

min. Z=38 Ohms

#### Vias

min. Z=44 Ohms

# Impedance tools

- Cadence Allegro SpectraQuest

- Mentor Graphics' Hyperlynx

- Missouri Univ. of Science & Tech. FEMAS

- IBM Yorktown EIP tools (CZ2D, EmitPkg)

- Polar Instruments (http://www.polarinstruments.com)

- HSPICE built-in field solver

- Ansys, Applied Simulation Technology, etc. field solvers

- Agilent AppCAD (http://www.agilent.com)

- Tektronix Iconnect<sup>tm</sup>

- other free tools

# Maximizing SI

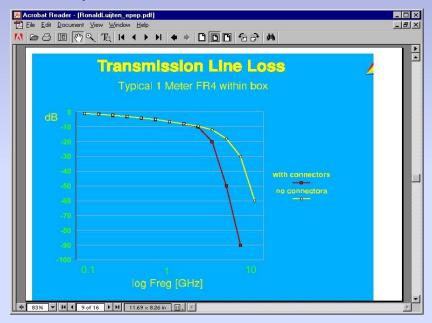

- Understand the channel

- Biggest culprit is frequency-dependent insertion loss (and reflections)

- Next problem is crosstalk

source: R. Luijten, IBM Zurich, 2000 EPEP Conf.

- Minimize channel losses, reflections, crosstalk

- Equalize if necessary

source: J. Cain, Cisco Systems, 2000 EPEP Conf.

#### Vector Network Analyzer

- Frequency-swept stimulus and response

- Two or more ports

- No location information

- Displays results in various formats

- Log magnitude/phase

- Smith Chart

- Time domain (w/ software)

#### References

- Agilent Technologies Application Note AN-1304: "Time Domain Reflectometry Theory"

- Blood, W. R., Jr.: MECL Systems Design Handbook (http://www.onsemi.com/home, look for HB205)

- Bogatin, E.: Signal Integrity Simplified, Prentice-Hall

- Bogatin, Corey, and Resso, M.: "Practical Characterization and Analysis of Lossy Transmission Lines," DesignCon 2001

- Bowick, C.: RF Circuit Design, Howard Sams, 1982

- Deutsch, A.: "Electrical Characteristics of Interconnections for High-Performance Systems," Proc. IEEE,

Feb. 1998

- EIA-364 Test Methods, Electronic Components Association, available at http://www.eca.com

- Hall, S. H., Hall, G. W., and McCall, J. A.: High-Speed Digital System Design: A Handbook of Interconnect Theory and Design Practices, Wiley

- Hewlett Packard Application Note 62, "TDR Fundamentals"

- Hewlett Packard Application Note 95-1, "S-Parameter Techniques for Faster, More Accurate Network Design"

- Hayt, W.: Engineering Electromagnetics, McGraw-Hill

- Johnson, H. and Graham, M.: High Speed Digital Design, Prentice-Hall

- Matick, R.: Transmission Lines for Digital and Communications Networks, IEEE Press

- Pozar, D.: Microwave Engineering Wiley, 2005

- Ramo, S., Whinnery, J., and Van Duzer, T.: Fields and Waves in Communication Electronics, Wiley

- Young, Brian: Digital Signal Integrity Modeling and Simulation with Interconnects and Packages, Prentice-Hall

- http://www.murata.com capacitor calculator

- <a href="http://www.te.com">http://www.te.com</a>, <a href="www.molex.com">www.molex.com</a> connector specs., papers on card wiring losses, via characteristics, etc.

4/8/2014 40

#### Conferences

- DesignCon February, in Santa Clara, CA

- IEEE Electrical Performance of Electronic Packaging (EPEP)

- IEEE EMC Symposium (EMCS)

- in Raleigh, NC in August, 2014

- Embedded SI conference

- http://www.emcs.org

- IEEE ECTC, ED, ISSCC

- IEEE SPI workshop (Europe)

#### Conclusion

Please fill out the online evaluation form at <a href="http://www.emcs-dl.org/DL\_Survey.php">http://www.emcs-dl.org/DL\_Survey.php</a>, using password EMCSDL

## Thank you!